Peripherals Routed Through the DAI

A-160 ADSP-214xx SHARC Processor Hardware Reference

18 SDEN_A Enable Channel A Serial Port DMA.

0 = Disable serial port channel A DMA

1 = Enable serial port channel A DMA

19 SCHEN_A Enable Channel A Serial Port DMA Chaining.

0 = Disable serial port channel A DMA chaining

1 = Enable serial port channel A DMA chaining

20 SDEN_B Enable Channel B Serial Port DMA.

0 = Disable serial port channel B DMA

1 = Enable serial port channel B DMA

21 SCHEN_B Enable Channel B Serial Port DMA Chaining.

0 = Disable serial port channel B DMA chaining

1 = Enable serial port channel B DMA chaining

22 Reserved

23 BHD Buffer Hang Disable.

0 = Indicates a core stall. The core stalls when it tries to write to a full

transmit buffer or read an empty receive buffer FIFO.

1 = Ignore a core hang

24 SPEN_B Enable Channel B Serial Port.

0 = Serial port A channel disabled

1 = Serial port A channel enabled

25 SPTRAN Data Direction Control. This bit controls the data direction of the

serial port channel A and B signals.

When cleared (= 0) the SPORT is configured to receive on both chan-

nels A and B. When configured to receive, the RXSPxA and RXSPxB

buffers are activated, while the receive shift registers are controlled by

SPORTx_CLK and SPORTx_FS. The TXSPxA and TXSPxB buffers

are inactive.

When set (= 1) the SPORT is configured to transmit on both channels

A and B. When configured to transmit, the TXSPxA and TXSPxB buf-

fers are activated, while the transmit shift registers are controlled by

SPORTx_CLK and SPORTx_FS. The RXSPxA and RXSPxB buffers

are inactive.

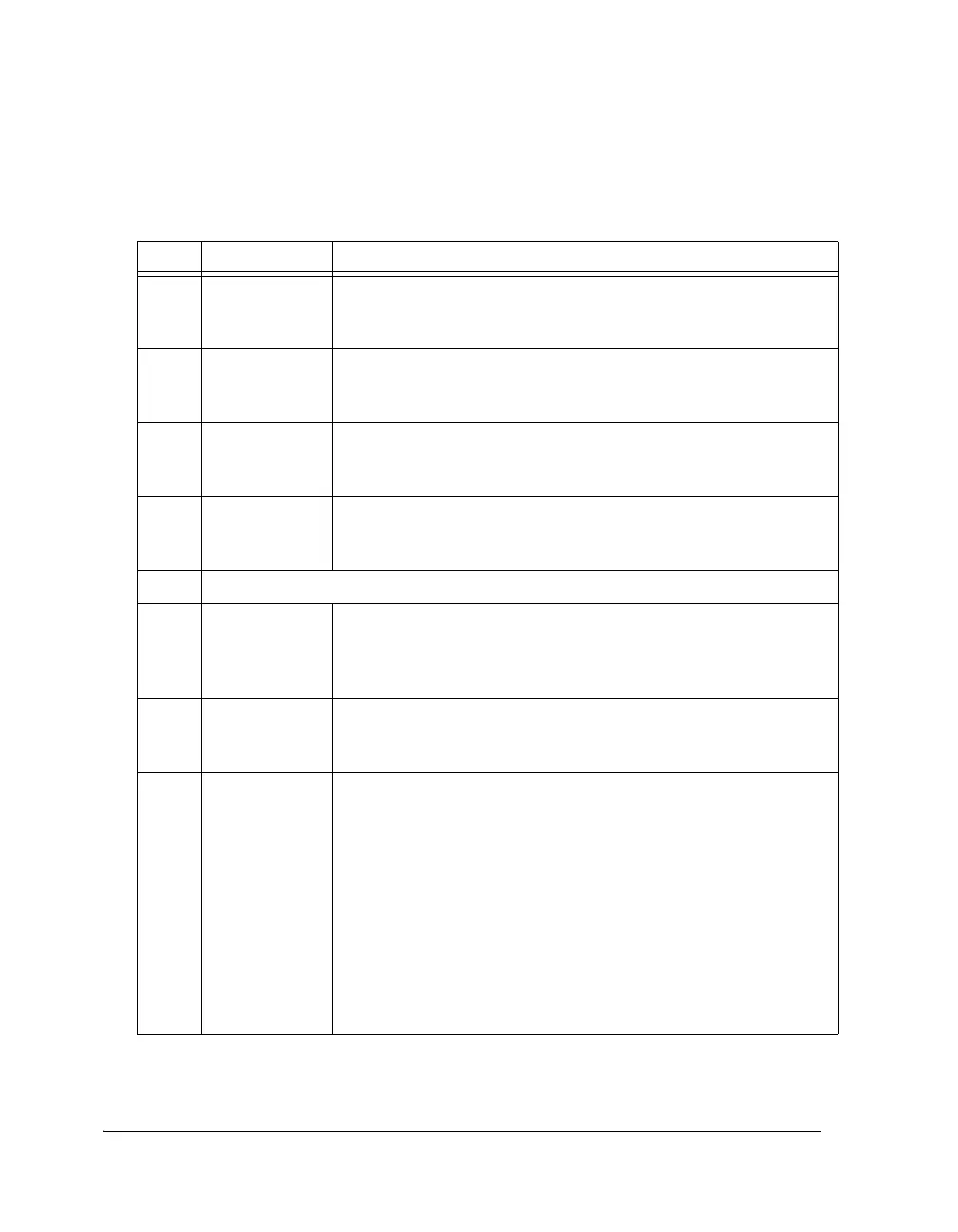

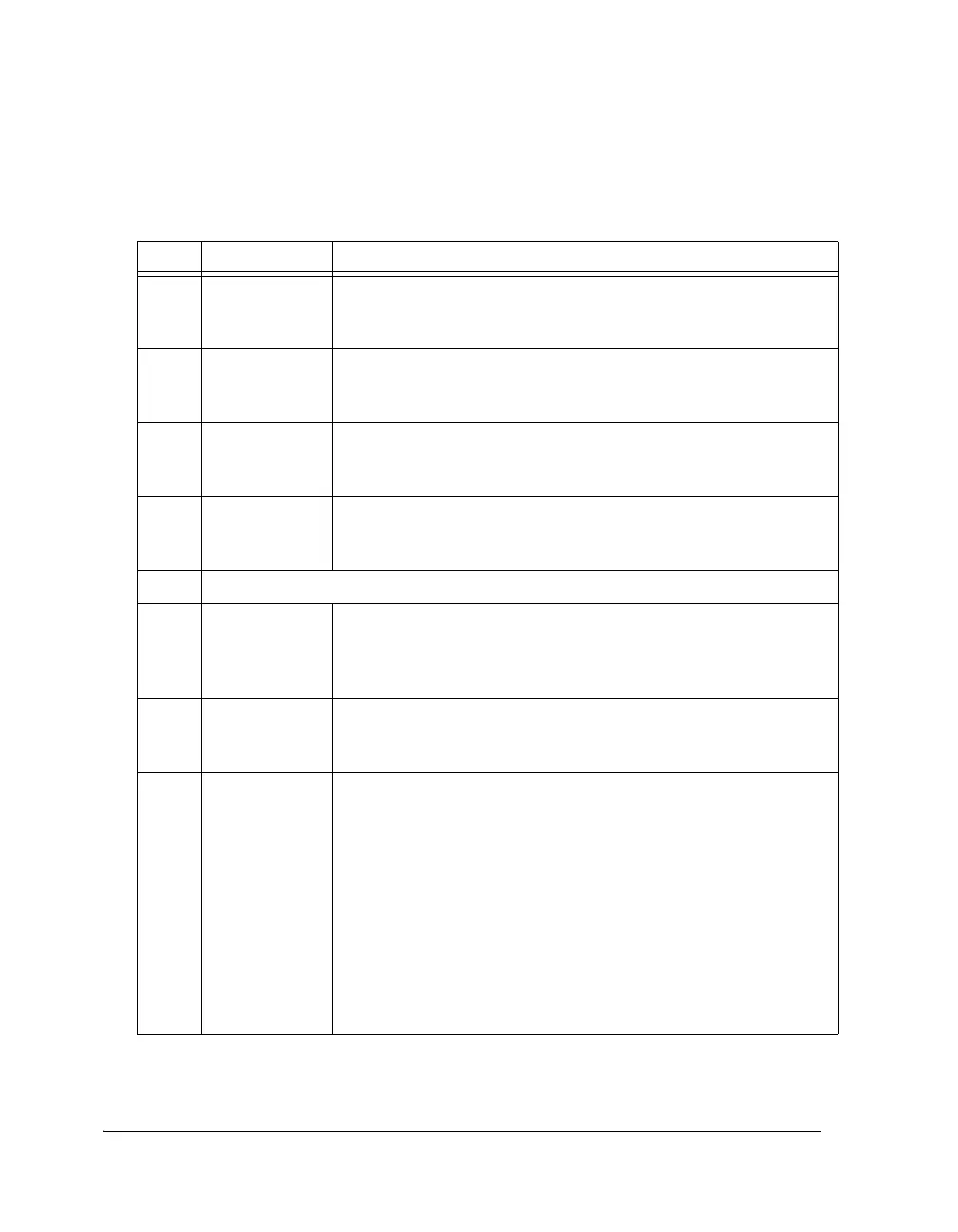

Table A-85. SPCTLx Register Bit Descriptions (I

2

S,

Left-Justified) (RW) (Cont’d)

Bit Name Description

Loading...

Loading...