Peripherals Routed Through the DAI

A-162 ADSP-214xx SHARC Processor Hardware Reference

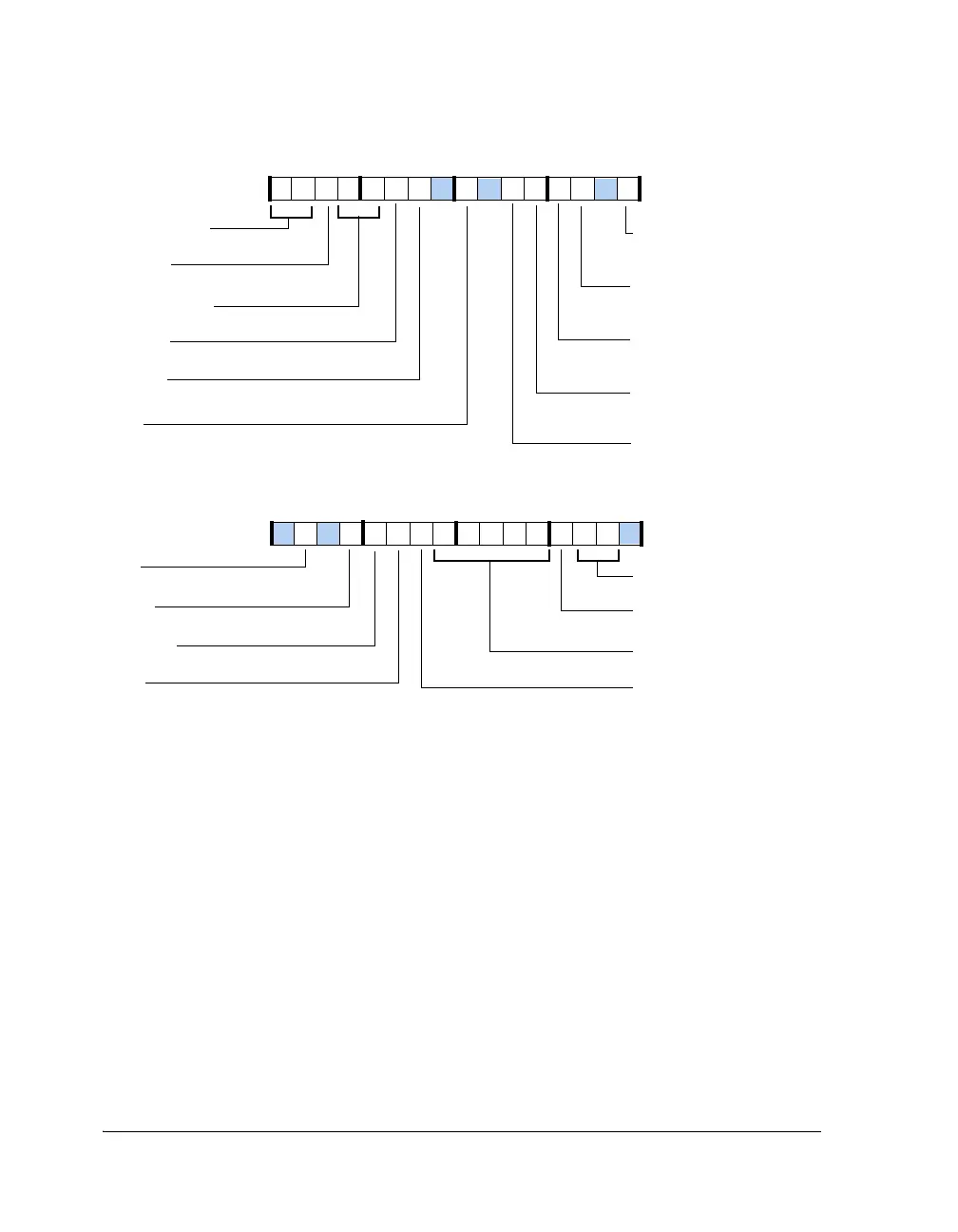

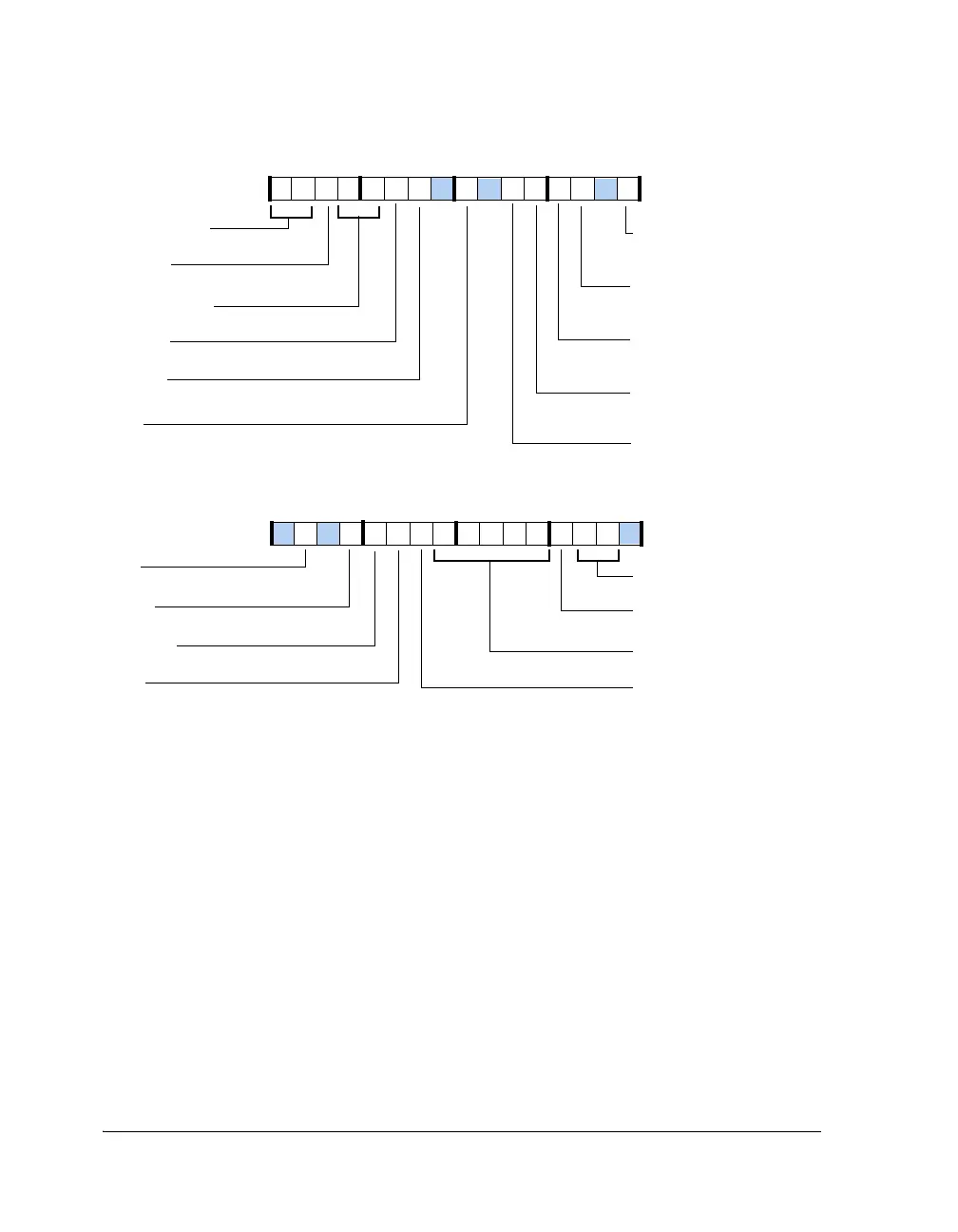

Figure A-88. SPCTLx Register – Packed and Multichannel Mode

DXS_A (31–30)

Data Buffer Channel A Status

LMFS/L_FIRST

Active Low Multichannel

Frame Sync Select/Channel

Order First

DERR_A

Channel A Error status

SDEN_A

SPORT DMA Channel

A Enable

DXS_B (28–27)

Data Buffer Channel B Status

DERR_B

BHD

Buffer Hang Disable

SCHEN_A

SPORT DMA Channel A

Chaining Enable

SDEN_B

SPORT DMA Channel B

Enable

SCHEN_B

SPORT DMA Channel B

Chaining Enable

Channel B Error Status

IFS

DTYPE (2–1)

Data Type

LSBF

Serial Word Bit Order

SLEN (8–4)

Serial Word Length

PACK

16/32 Packing

Internal Frane Sync Select

CKRE

Clock Rising Edge Select

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

SPTRAN

SPORT Data Direction

OPMODE

SPORT Operation Mode

ICLK

Internal Clock Select

Loading...

Loading...