ADSP-214xx SHARC Processor Hardware Reference 2-5

I/O Processor

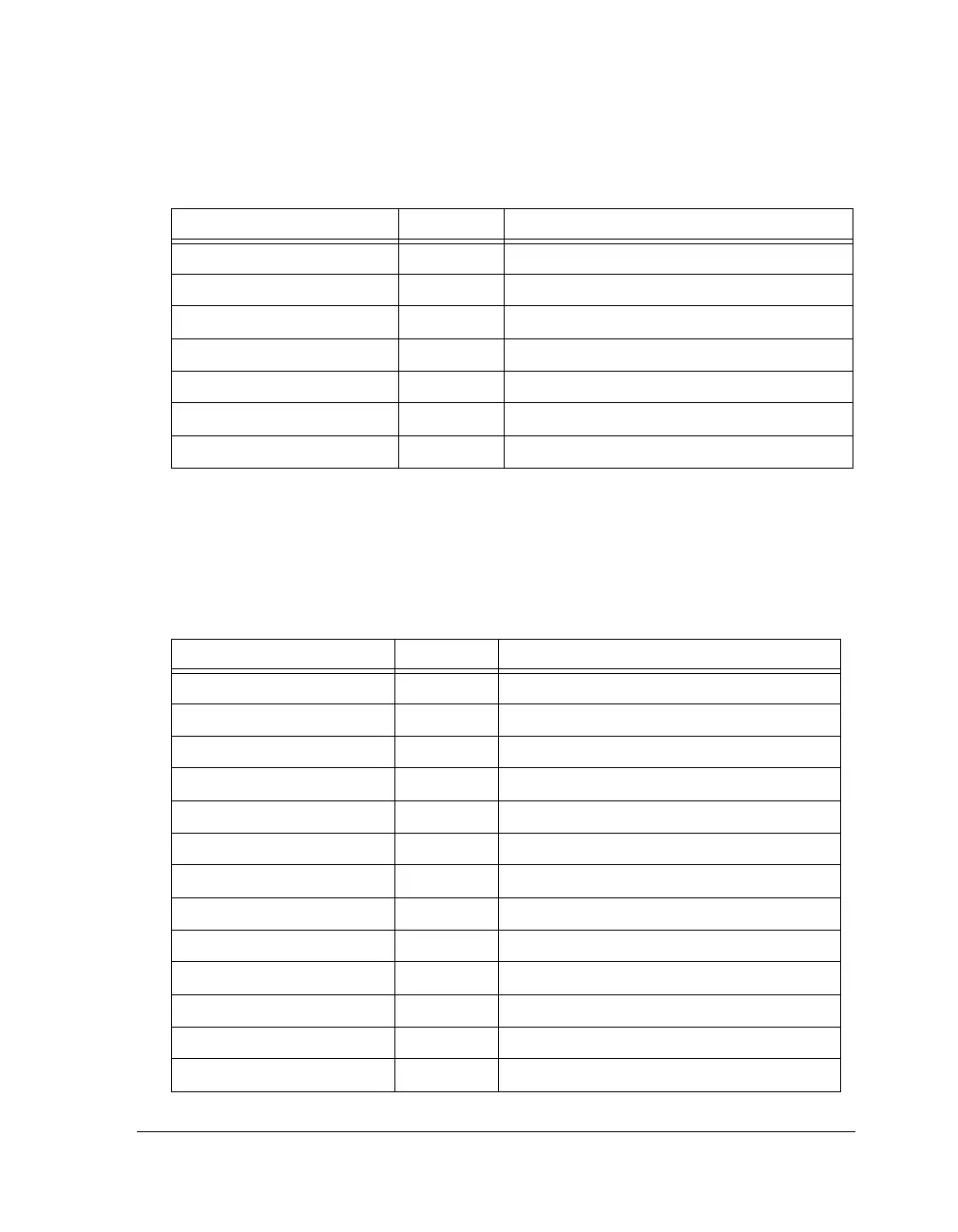

Modify registers. These registers, shown in Table 2-3, provide the signed

increment by which the DMA controller post-modifies the corresponding

memory index register after the DMA read or write.

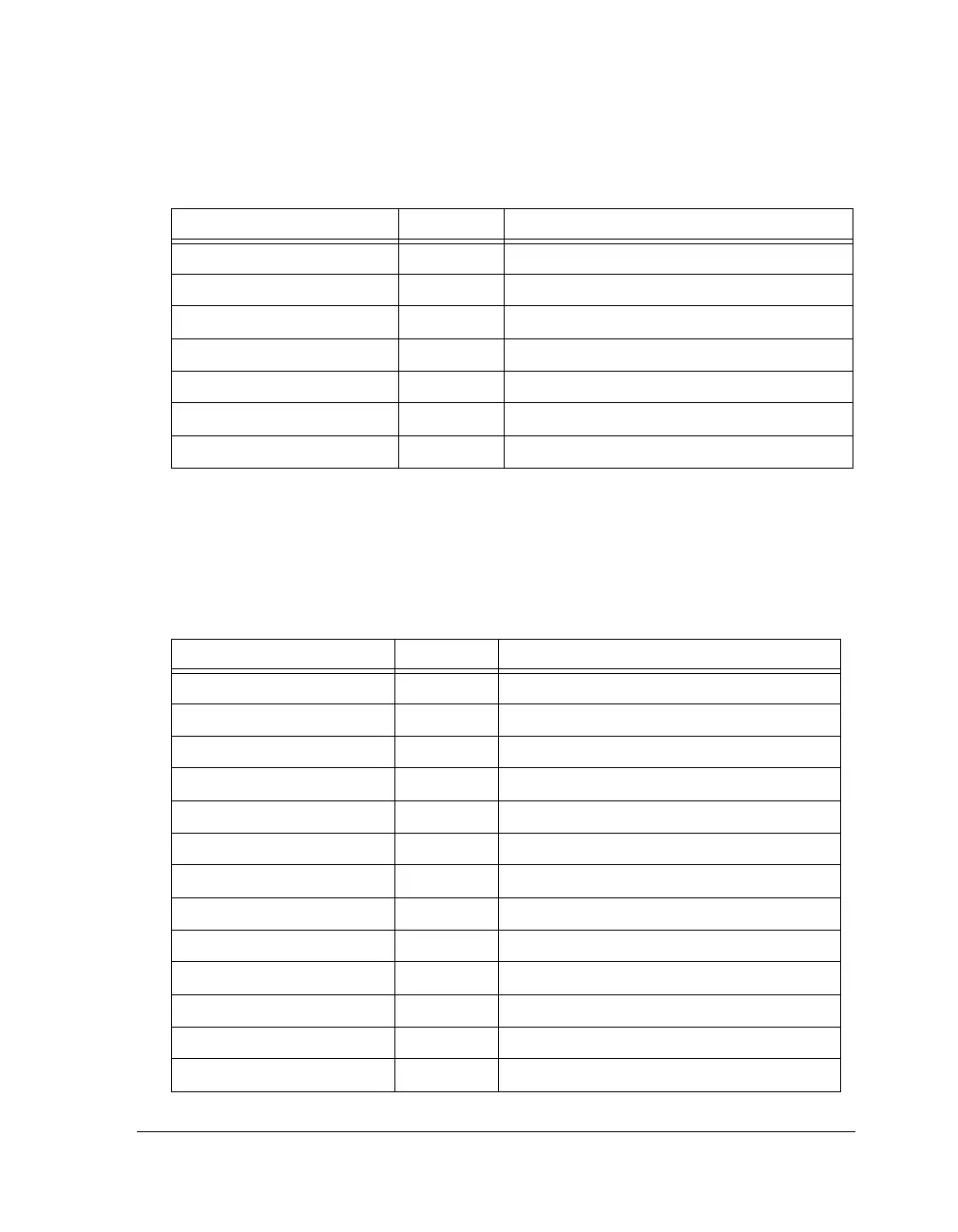

OIIIR 19 Accelerator IIR output

IIFFT 19 Accelerator FFT input

OIFFT 19 Accelerator FFT output

IIMTMW 19 MTM Write

IIMTMR 19 MTM Read

IIEP0–1 19 External Port0–1

EIEP0–1 28 External Port (external)

Table 2-3. Modify Registers

Register Name Width (Bits) Description

IMSP0–7A 16 SPORTA

IMSP0–7B 16 SPORTB

IMSPI 16 SPI

IMSPIB 16 SPIB

IDP_DMA_M0–7 6 IDP

IDP_DMA_M0–7A 6 IDP modify A (ping pong)

IDP_DMA_M0–7B 6 IDP modify B (ping pong)

IMLB0–1 16 Link Port

IMUART0RX 16 UART0 Receiver

IMUART0TX 16 UART0 Transmitter

IMFIR 16 Accelerator FIR data input

CMFIR 16 Accelerator FIR coeff input

OMFIR 16 Accelerator FIR output

Table 2-2. Index Registers (Cont’d)

Register Name Width (Bits) Description

Loading...

Loading...