ADSP-214xx SHARC Processor Hardware Reference A-49

Registers Reference

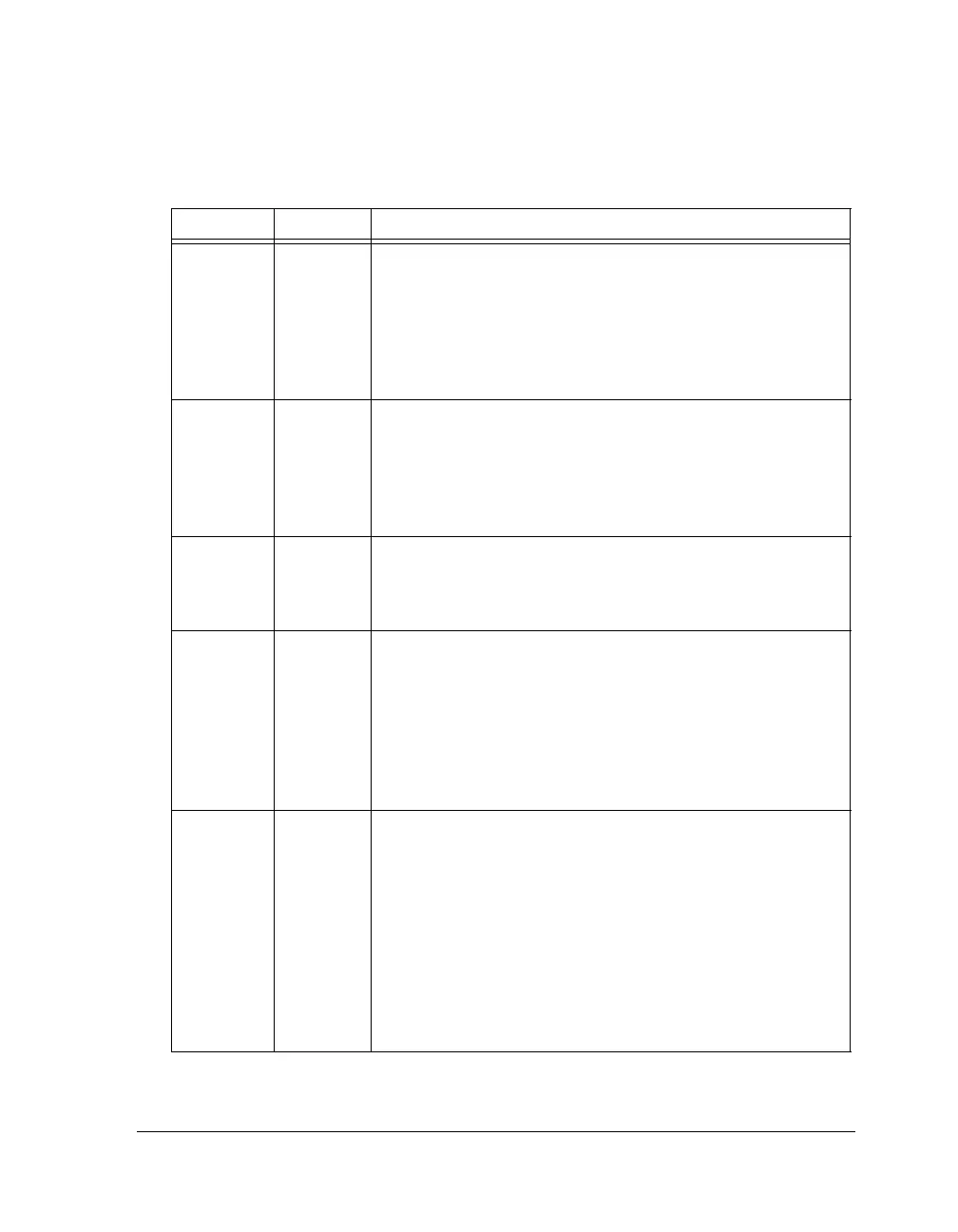

3PKDISDisable Packing/Unpacking.

0 = 8/16-bit data received packed to 32-bit data. Similarly, 32-bit

data to be transmitted is unpacked to four 8-bit data.

1 = 8/16-bit data received zero-filled, for transmitted data only

8-bit LSB part of the 32-bit data is written to external memory.

Note this bit should not be set for bank 0 which is to be used for

instruction fetch.

4MSWFMost Significant Word First. Applicable only with packing disabled

(PKDIS=0).

0 = 1st 8/16-bit word read/write occupies the least significant posi-

tion in the 32-bit packed word.

1 = 1st 8/16-bit word read/write occupies the most significant posi-

tion in the 32-bit packed word.

5ACKENEnable the ACK pin. If enabled, reads/writes to devices must be

extended by the corresponding devices by pulling ACK low. When

ACKEN is set, then the ACK pin is sampled after the wait state

value is programmed.

10–6 WS Wait States.

00000 = Reserved (wait state value of 32 if used)

00001 = wait state=1 (only if ACK input used)

00010 = wait state = 2

11111 = Wait state = 31

Wait states and acknowledge signals are used to allow the processors

to connect to memory-mapped peripherals and slower memories.

Wait states are programmable from 1 to 31.

13–11 HC Bus Hold Cycle at the End of Write Access.

000 = Disable bus hold cycle

001 = Hold address for one external port clock cycle

010 = Hold address for two external port clock cycles

A bus hold cycle is an inactive bus cycle that the processor automat-

ically generates at the end of a write to allow a longer hold time for

address and data. Programs may disable holds, or hold off process-

ing for one or more external port processor cycles. Note the address,

data (if a write), and bank select (if in banked external memory)

remain unchanged and are driven for one or more cycles after the

read or write strobes are deasserted.

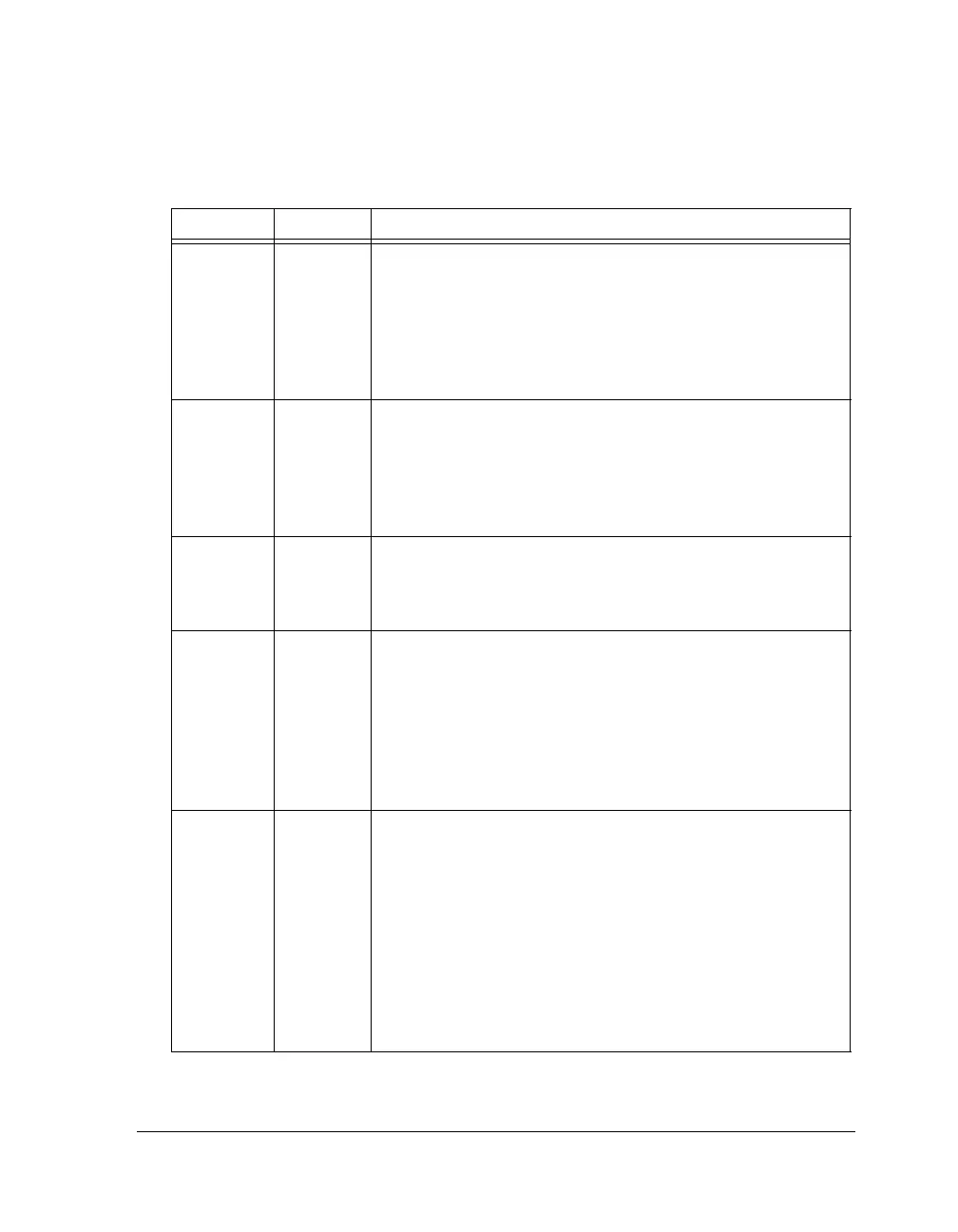

Table A-26. AMICTLx Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...