ADSP-214xx SHARC Processor Hardware Reference A-105

Registers Reference

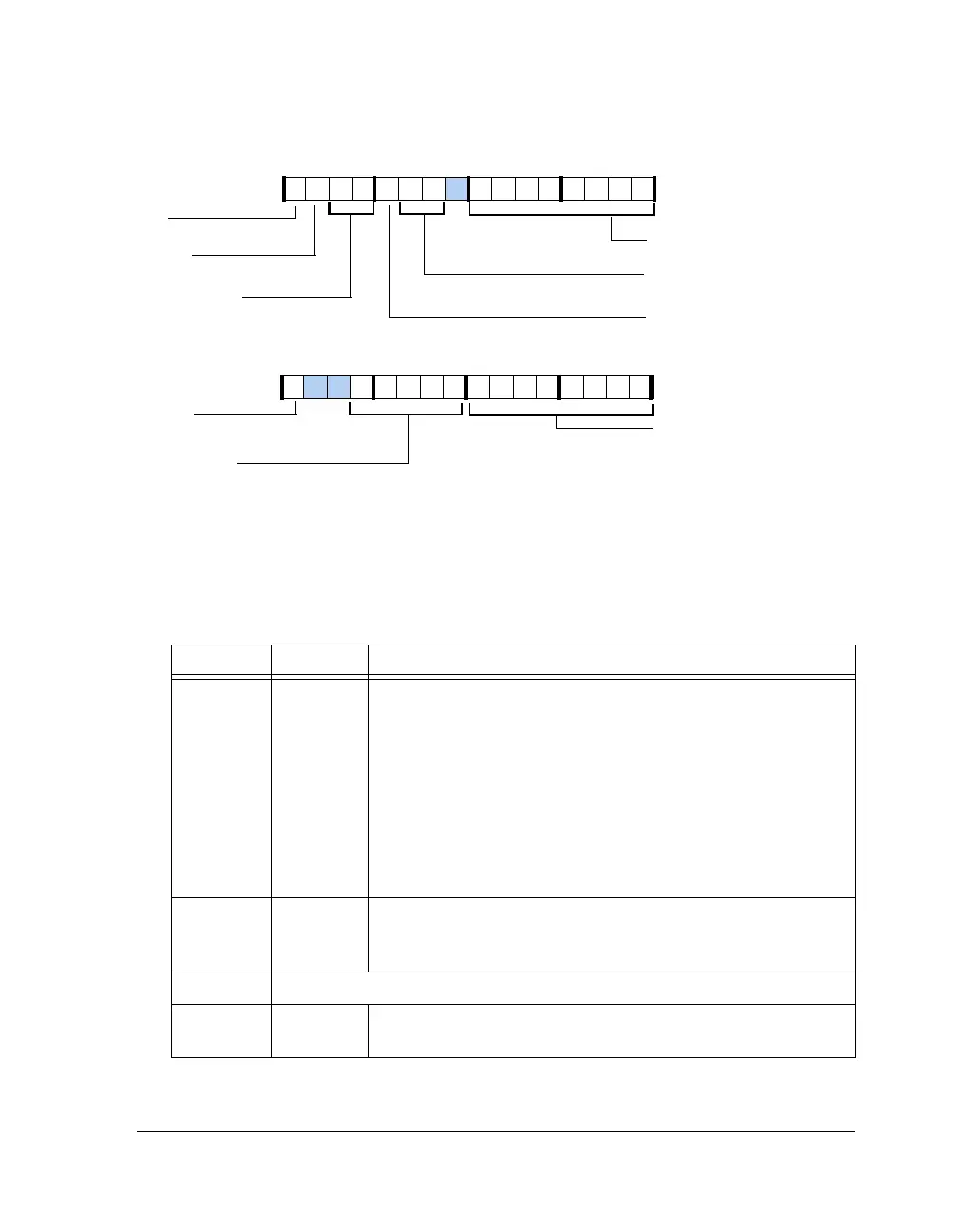

Figure A-49. MLB_CECRx Register (Synchronous Channels)

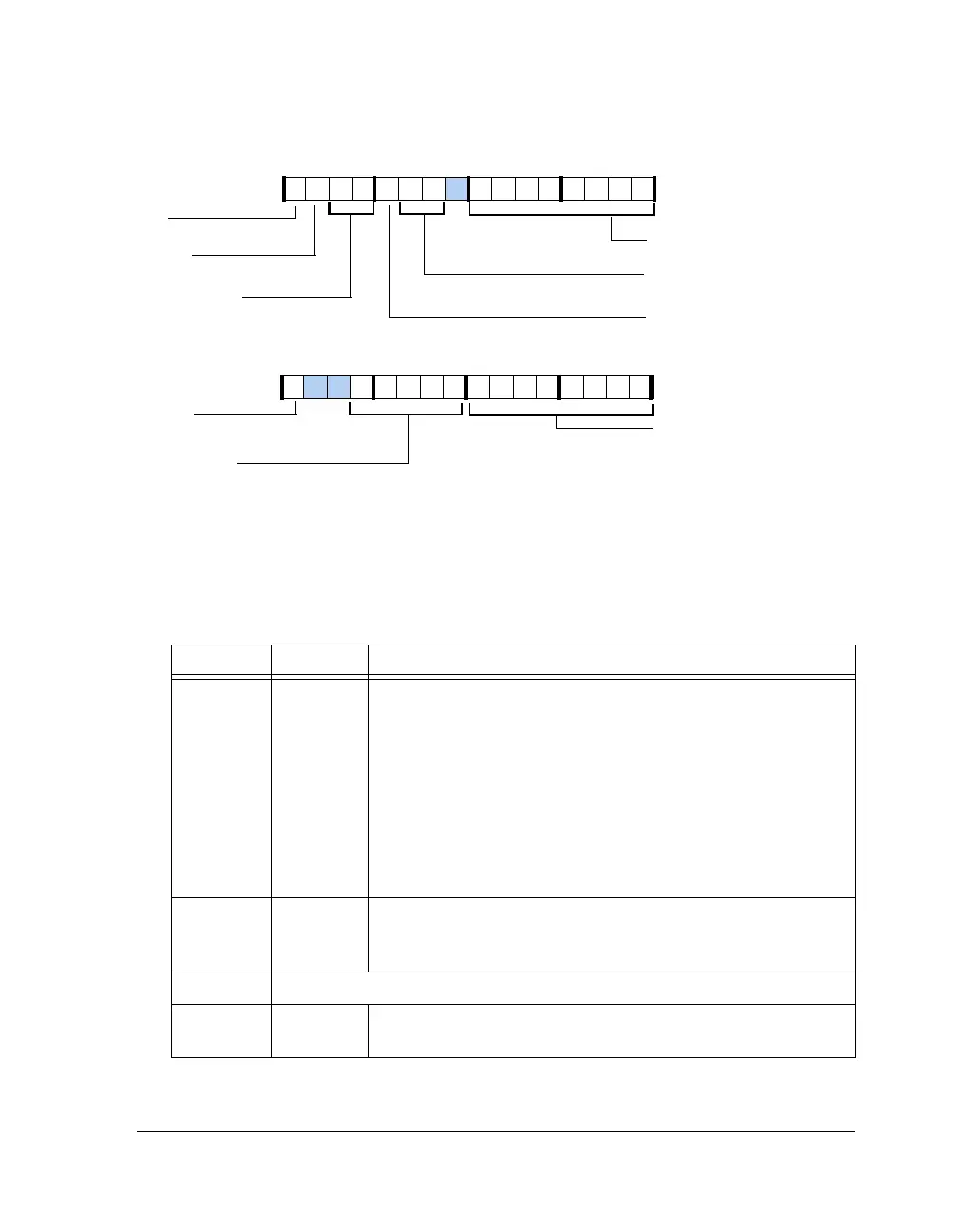

Table A-67. MLB_CECRx Register Bit Descriptions for Synchronous

Channels (RW)

Bit Name Description

7–0 CA Channel Address. These bits determine the channel address associ-

ated with this logical channel. MLB channel address is 16 bits; bits

15–9 and LSB are always zero. Only bits 8–1 vary and they are

defined by MLB_CECRx bits 7–0.

00000001 0x0002

00000010 0x0004

00000011 0x0006

00000100 0x0008

.............

11111111 0x01FE

12–8 FSPC Frame Synchronization Physical Channel Count. Defines the num-

ber of physical channels expected to match this logical channel’s

channel address each MLB frame.

14–13 Reserved

15 FSCD Frame Synchronization Channel Disable. When set, disables this

logical channel when frame synchronization is lost.

CA (7–0)

Channel Address

FSPC (12–8)

Frame Synchronization Physi-

cal Channel Count

CE

Frame Synchronization

Enable

MDS

Channel x Mode Select

CTYPE (29–28)

MASK (23–16)

Channel x Interrupt Mask

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

CTRAN

FSE

Channel x Enable

Channel x Transmit Select

Channel x Type Select

Frame Synchronization

Channel Disable

FSCD

Loading...

Loading...