ADSP-214xx SHARC Processor Hardware Reference A-125

Registers Reference

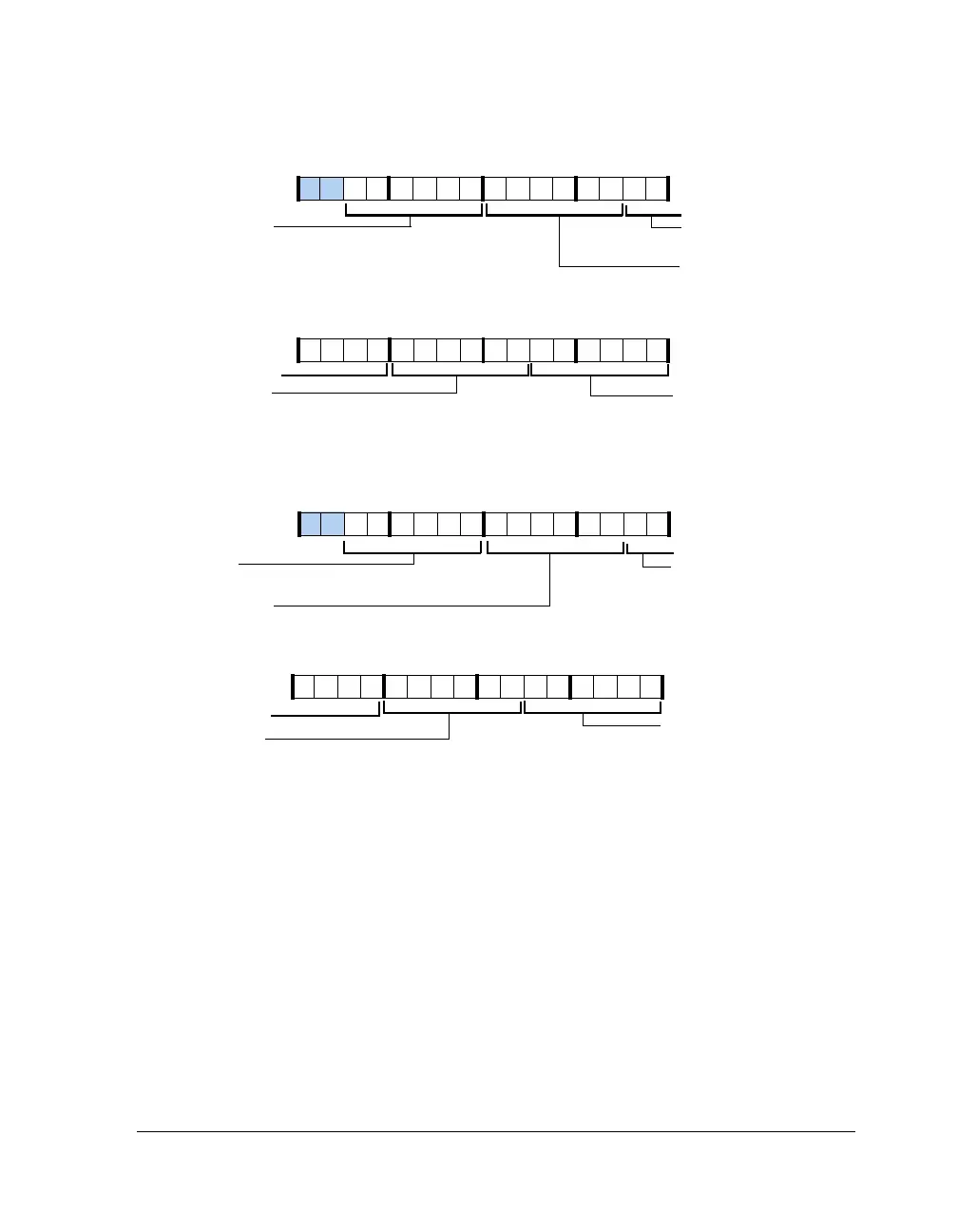

Figure A-62. SRU_DAT4 Register (RW)

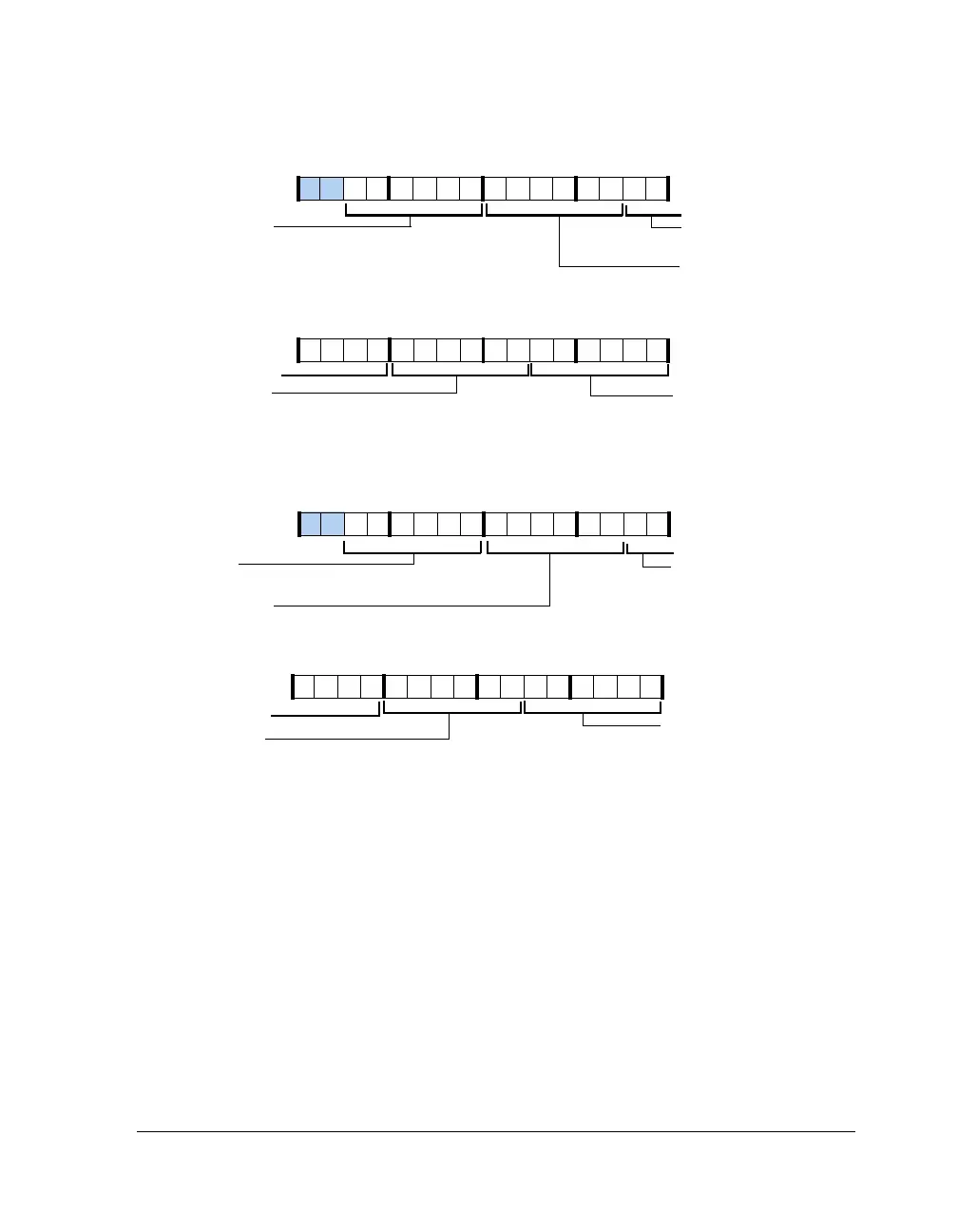

Figure A-63. SRU_DAT5 Register (RW)

SPDIF Transmit Data

Input

DIT_DAT_I (5–0)

IDP2_DAT_I (23–18)

Input Data Port 2

Data Input

IDP3_DAT_I (29–24)

Input Data Port 3 Data Input

IDP0_DAT_I (11–6)

Input Data Port 0 Data Input

IDP1_DAT_I (17–12)

Input Data Port 1 Data Input

IDP1_DAT_I (17–12) (con’t)

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Input Data Port 4 Data

Input

IDP4_DAT_I (0–5)

IDP6_DAT_I (17–12) (con’t)

IDP7_DAT_I (23–18)

Input Data Port 7 Data Input

IDP5_DAT_I (11–6)

Input Data Port 5 Data Input

IDP6_DAT_I (17–12)

Input Data Port 6 Data Input

DIR_I (29–24)

SPDIF Biphase Receiver Stream

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Loading...

Loading...