DAI Signal Routing Unit Registers

A-130 ADSP-214xx SHARC Processor Hardware Reference

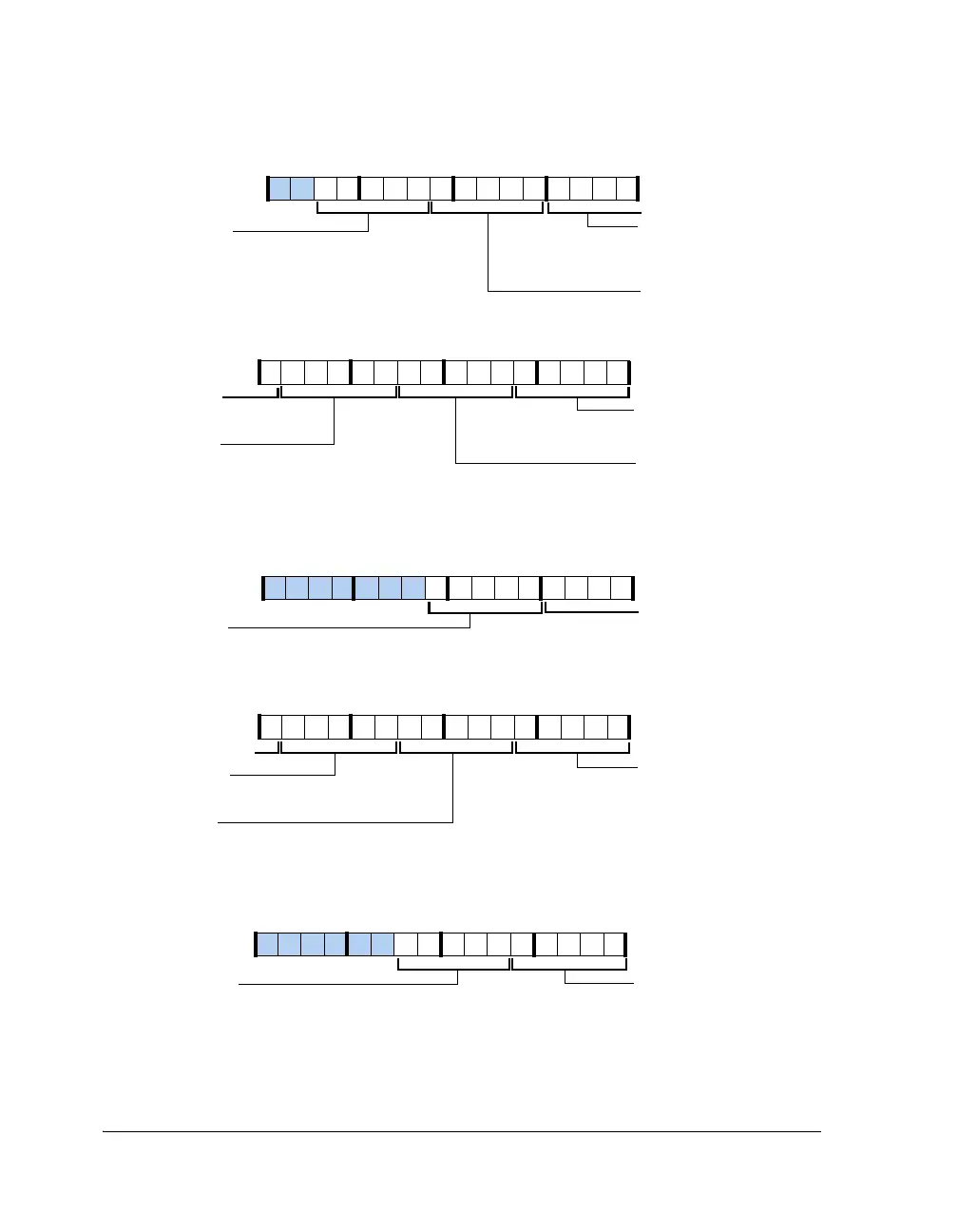

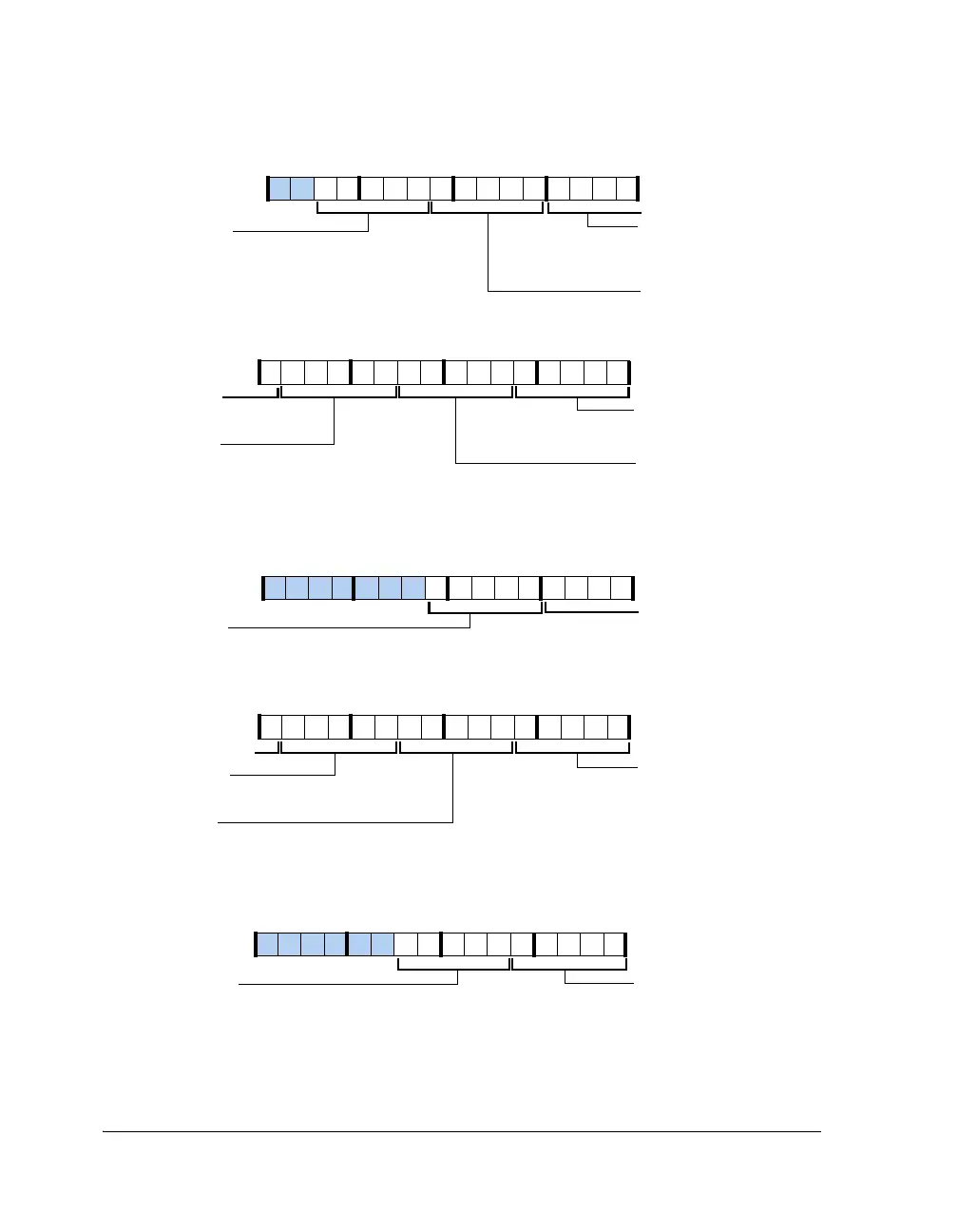

Figure A-67. SRU_FS2 Register (RW)

Figure A-68. SRU_FS3 Register (RW)

Figure A-69. SRU_FS4 Register (RW)

IDP2_FS_I (29–25)

DIT_FS_I (14–10)

IDP0_FS_I or

PDAP_HOLD_I (19–15)

(con’t)

IDP0_FS_I or

PDAP_HOLD_I

(19–15)

SRC3 _FS_IP_I (4–0)

SRC3 _FS_OP_I (9–5)

IDP1_FS_I (24–20)

Sample Rate Converter 3

Frame Sync Input Input

Input Data Port Channel 1

Frame Sync Input

Input Data Port Channel

0 Frame S ync Input

Input Data Port Channel 2

Frame Sync Input

Sample Rate Converter 3

Frame Sync Output Input

SPDIF 3 Oversampling

Clock Input

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Input Data Port

Channel 7 Frame Sync Input

IDP7_FS_I (24–20)

IDP5_FS_I (14–10)

Input Data Port

Channel 6 Frame Sync Input

IDP6_FS_I (19–15) (con’t)

Input Data Port Channel 5

Frame S ync Input

IDP4_FS_I (9–5)

Input Data Port Channel 4

Frame S ync Input

Input Data Port

Channel 3 Frame Sync Input

IDP3_FS_I (4–0)

IDP6_FS_I (19–15)

31 302928 27 26 25 24 23 22 21 20 19 18 17 16

09 837564 2114 12 11 101315

Serial Port 6 Frame

Sync Input

SPORT6_FS_I (4–0)

Serial Port 7 Frame Sync Input

SPORT7_FS_I (9–5)

09 837564 2114 12 11 101315

Loading...

Loading...