TCB Storage

2-20 ADSP-214xx SHARC Processor Hardware Reference

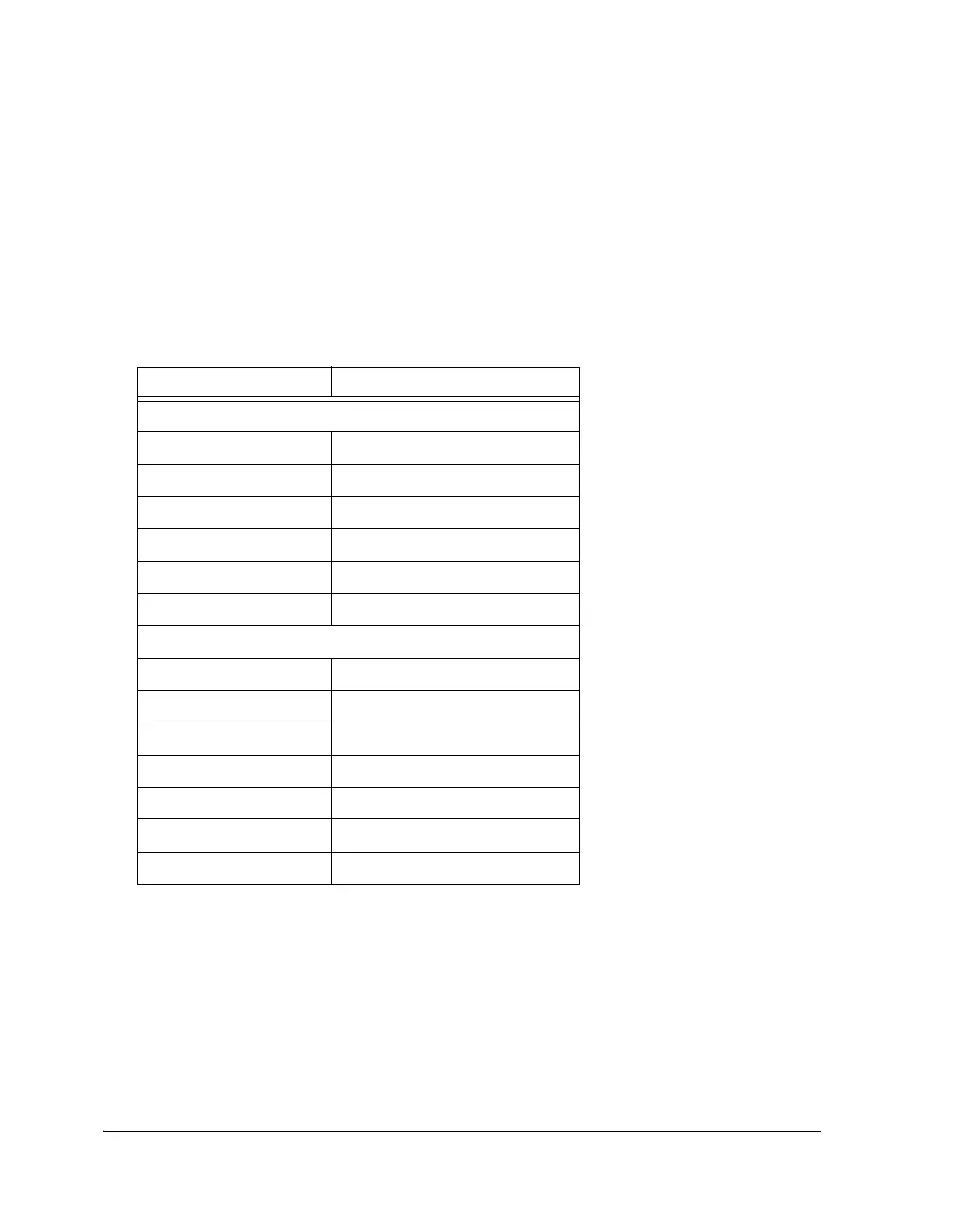

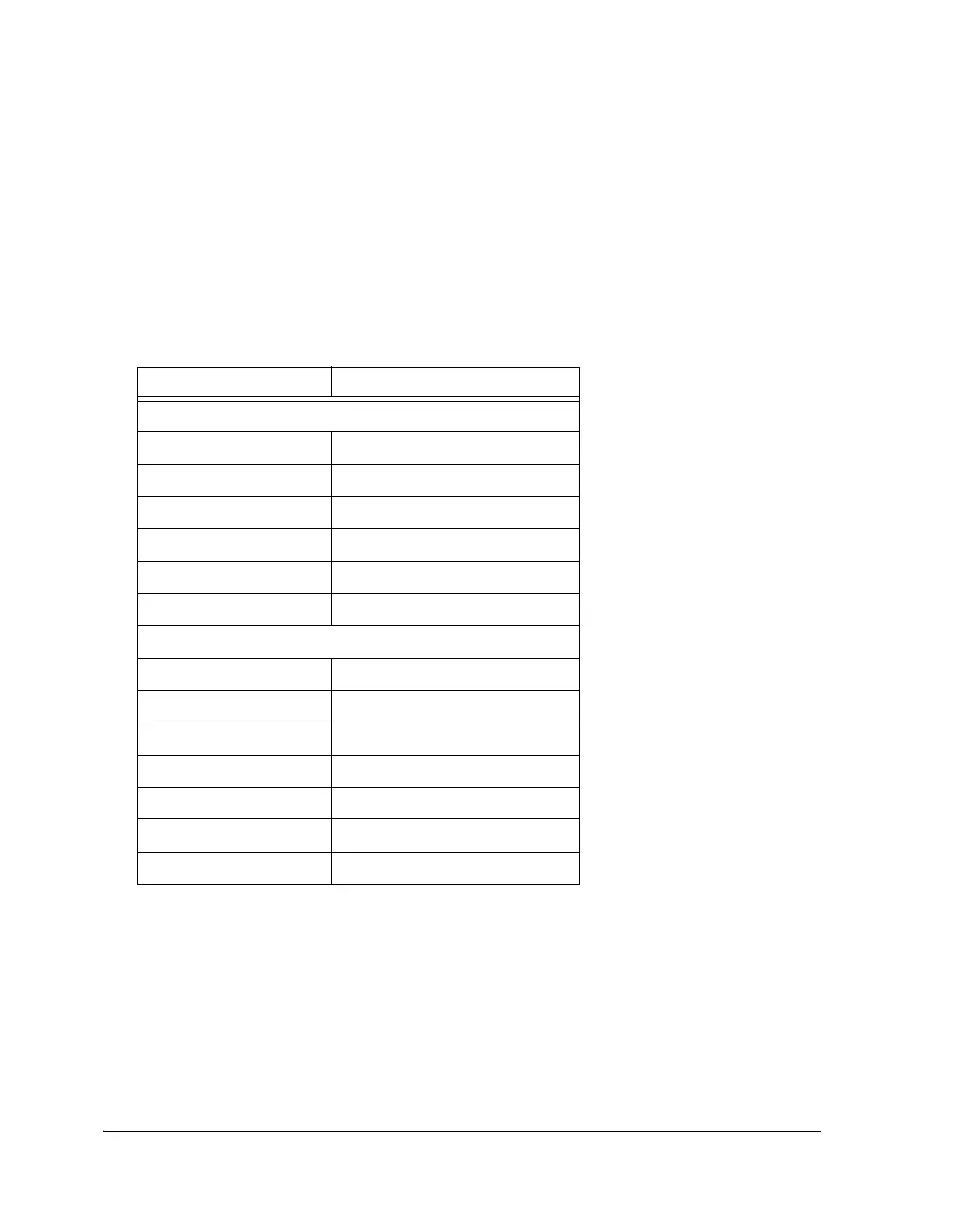

For delay line DMA, TCB loading is split into two sequences to improve

overall priority. The first TCB loads the write parameters (

IIEP–ELEP) and

the second loads the read parameters (RIEP–CPEP). This two stage loading

is transparent to the application. The order the descriptors are fetched

with circular buffering enabled is shown in Table 2-24.

Table 2-24. External Port TCBs for Delay Line DMA

Address Register

Delay Line Read

CP[18:0] CPEP

CP[18:0] + 0x1 TPEP

CP[18:0] + 0x2 TCEP

CP[18:0] + 0x3 RMEP

CP[18:0] + 0x4 RCEP

CP[18:0] + 0x5 RIEP

Delay Line Write

CP[18:0] + 0x6 ELEP

CP[18:0] + 0x7 EBEP

CP[18:0] + 0x8 EMEP

CP[18:0] + 0x9 EIEP

CP[18:0] + 0xA ICEP

CP[18:0] + 0xB IMEP

CP[18:0] + 0xC IIEP

Loading...

Loading...