EDMA3 Registers

www.ti.com

11.4.2.5.2 Error Enable Register (ERREN)

The error enable register (ERREN) is shown in Figure 11-110 and described in Table 11-95.

When any of the enable bits are set, a bit set in the corresponding ERRSTAT causes an assertion of the

EDMA3TC interrupt.

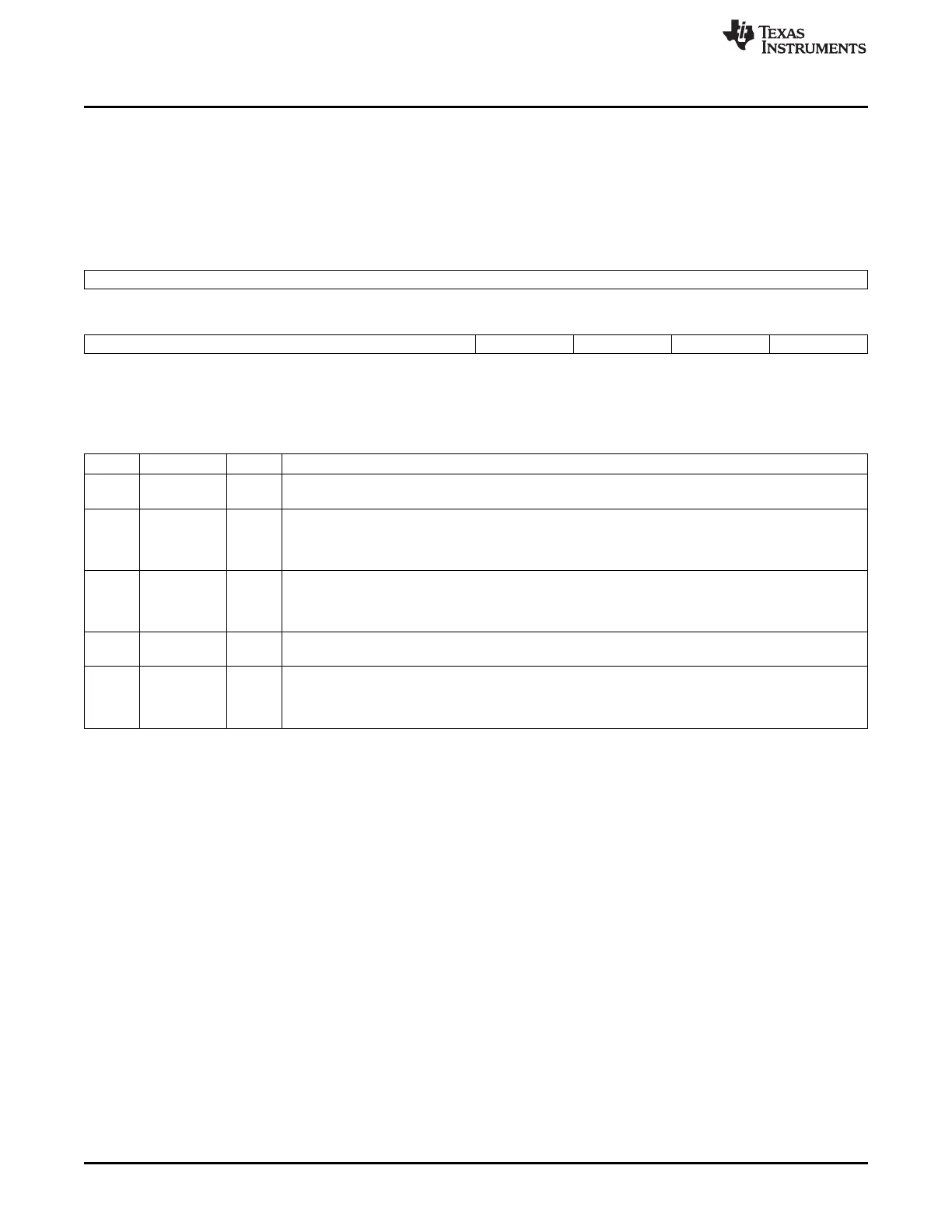

Figure 11-110. Error Enable Register (ERREN)

31 16

Reserved

R-0

15 4 3 2 1 0

Reserved MMRAERR TRERR Reserved BUSERR

R-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

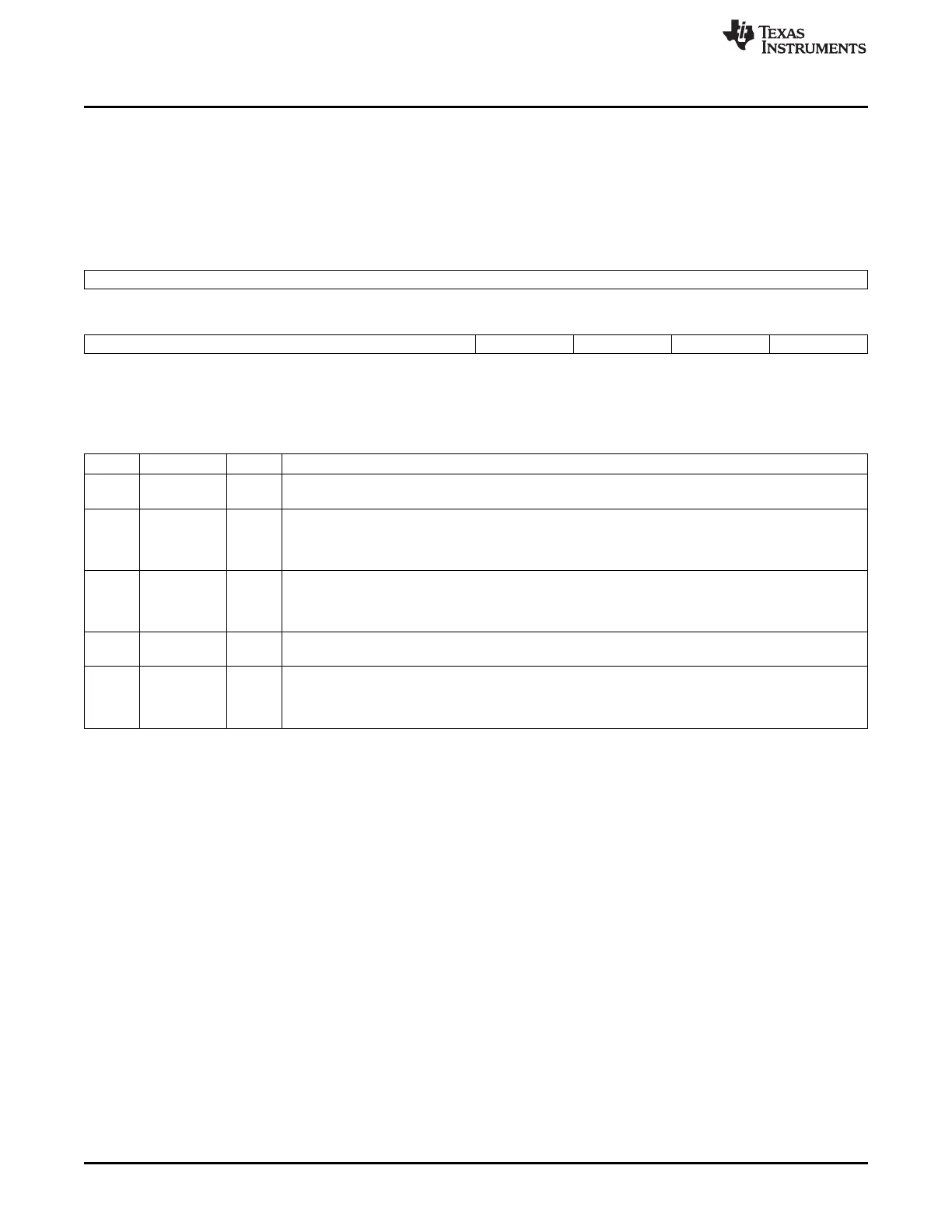

Table 11-95. Error Enable Register (ERREN) Field Descriptions

Bit Field Value Description

31-4 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

3 MMRAERR Interrupt enable for MMR address error (MMRAERR).

0 MMRAERR is disabled.

1 MMRAERR is enabled and contributes to the state of EDMA3TC error interrupt generation

2 TRERR Interrupt enable for transfer request error (TRERR).

0 TRERR is disabled.

1 TRERR is enabled and contributes to the state of EDMA3TC error interrupt generation.

1 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

0 BUSERR Interrupt enable for bus error (BUSERR).

0 BUSERR is disabled.

1 BUSERR is enabled and contributes to the state of EDMA3TC error interrupt generation.

1000

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...