www.ti.com

Ethernet Subsystem Registers

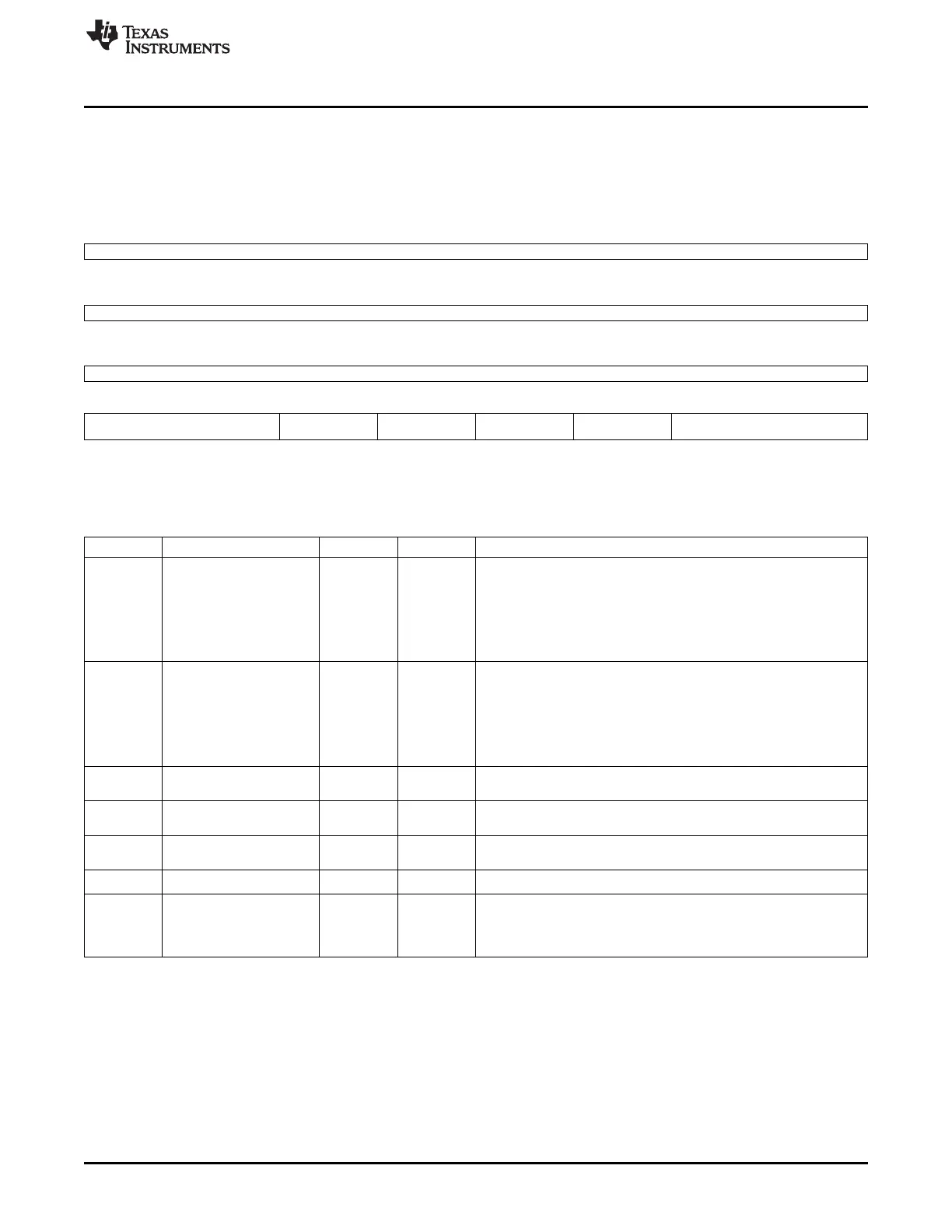

14.5.1.14 PORTCTL5 Register (offset = 54h) [reset = 0h]

PORTCTL5 is shown in Figure 14-28 and described in Table 14-38.

ADDRESS LOOKUP ENGINE PORT 5 CONTROL REGISTER

Figure 14-28. PORTCTL5 Register

31 30 29 28 27 26 25 24

BCAST_LIMIT

R/W-0

23 22 21 20 19 18 17 16

MCAST_LIMIT

R/W-0

15 14 13 12 11 10 9 8

Reserved

7 6 5 4 3 2 1 0

Reserved NO_SA_UPDATE NO_LEARN VID_INGRESS_CHE DROP_UNTAGGED PORT_STATE

CK

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

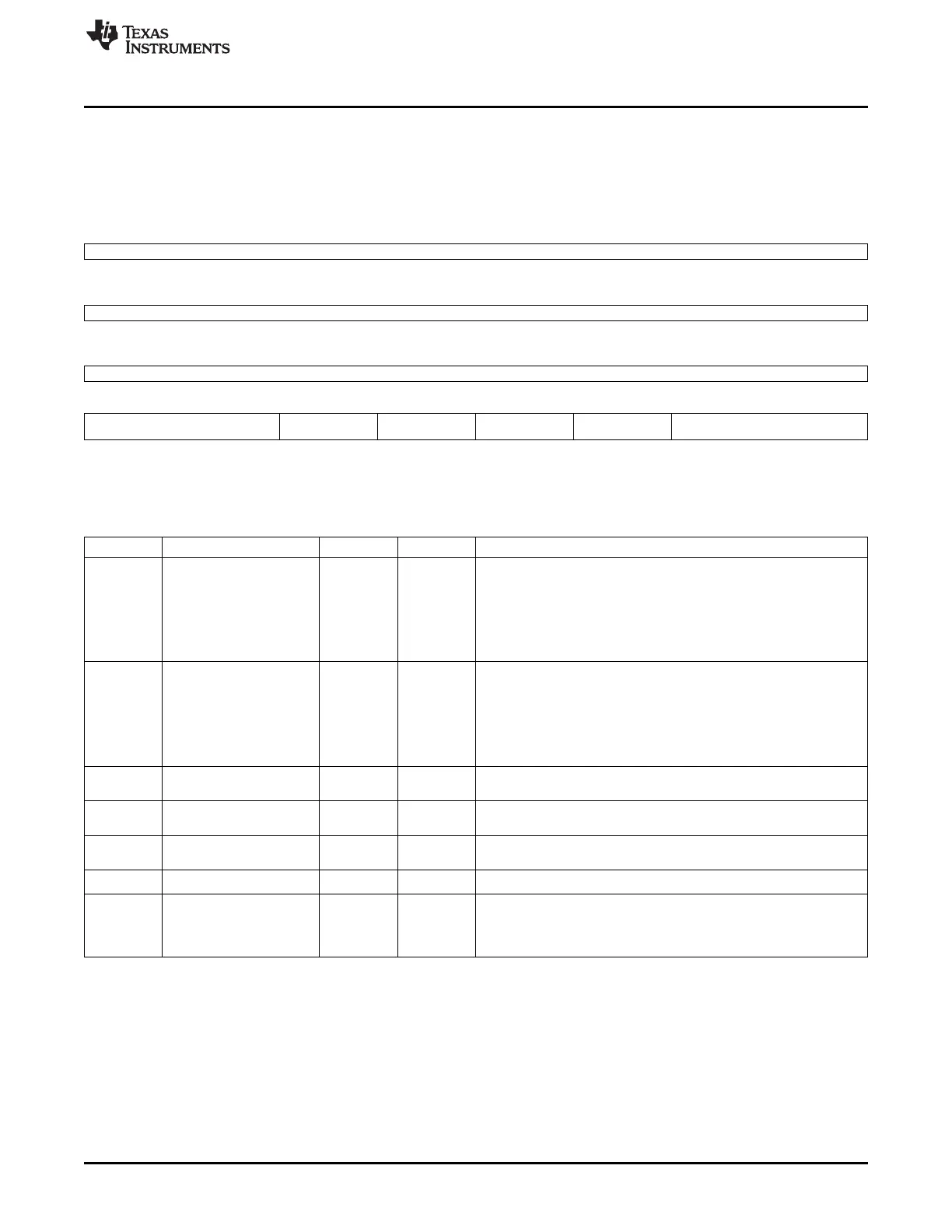

Table 14-38. PORTCTL5 Register Field Descriptions

Bit Field Type Reset Description

31-24 BCAST_LIMIT R/W-0 0 Broadcast Packet Rate Limit - Each prescale pulse loads this field

into the port broadcast rate limit counter.

The port counters are decremented with each packet received or

transmitted depending on whether the mode is transmit or receive.

If the counters decrement to zero, then further packets are rate

limited until the next prescale pulse.

Broadcast rate limiting is enabled by a non-zero value in this field

23-16 MCAST_LIMIT R/W-0 0 Multicast Packet Rate Limit - Each prescale pulse loads this field into

the port multicast rate limit counter.

The port counters are decremented with each packet received or

transmitted depending on whether the mode is transmit or receive.

If the counters decrement to zero, then further packets are rate

limited until the next prescale pulse.

Multicast rate limiting is enabled by a non-zero value in this field.

5 NO_SA_UPDATE R/W-0 0 No Souce Address Update - When set the port is disabled from

updating the source port number in an ALE table entry.

4 NO_LEARN R/W-0 0 No Learn Mode - When set the port is disabled from learning an

address.

3 VID_INGRESS_CHECK R/W-0 0 VLAN ID Ingress Check - If VLAN not found then drop the packet.

Packets with an unknown (default) VLAN will be dropped.

2 DROP_UNTAGGED R/W-0 0

Drop Untagged Packets - Drop non-VLAN tagged ingress packets.

1-0 PORT_STATE R/W-0 0 Port State

0 - Disabled

1 - Blocked

2 - Learn

14.5.2 CPSW_CPDMA Registers

Table 14-39 lists the memory-mapped registers for the CPSW_CPDMA. All register offset addresses not

listed in Table 14-39 should be considered as reserved locations and the register contents should not be

modified.

1255

SPRUH73H–October 2011–Revised April 2013 Ethernet Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...