www.ti.com

GPMC

7.1.3.3.1 GPMC Clock Configuration

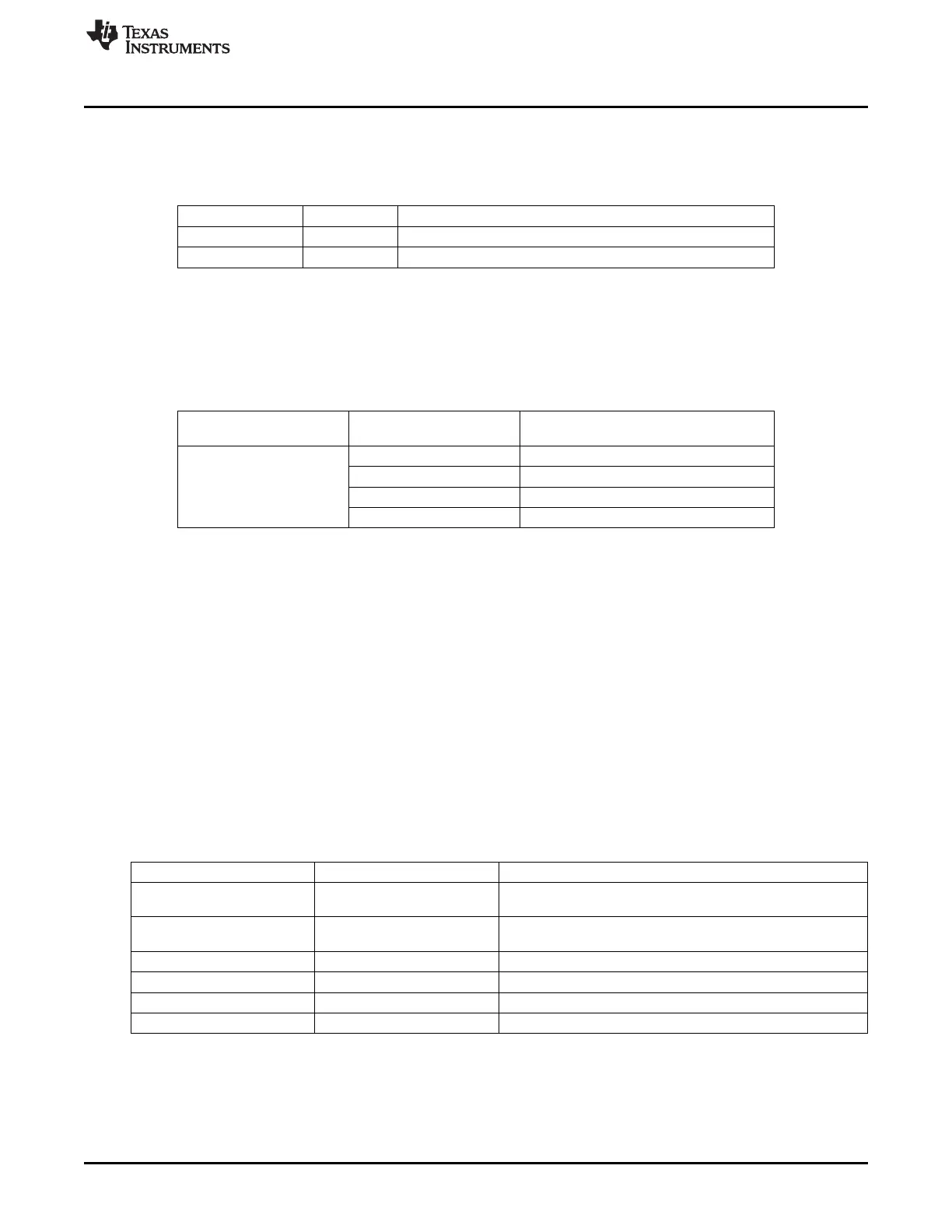

Table 7-6 describes the GPMC clocks.

Table 7-6. GPMC Clocks

Signal I/O Description

GPMC_FCLK I Functional and interface clock

GPMC_CLK O External clock provided to synchronous external memory devices.

The GPMC_CLK is generated by the GPMC from the internal GPMC_FCLK clock. The source of the

GPMC_FCLK is described in Table 7-3. The GPMC_CLK is configured via the GPMC_CONFIG1_i[1-0]

GPMCFCLKDIVIDER field (for i = 0 to 3) as shown in Table 7-7.

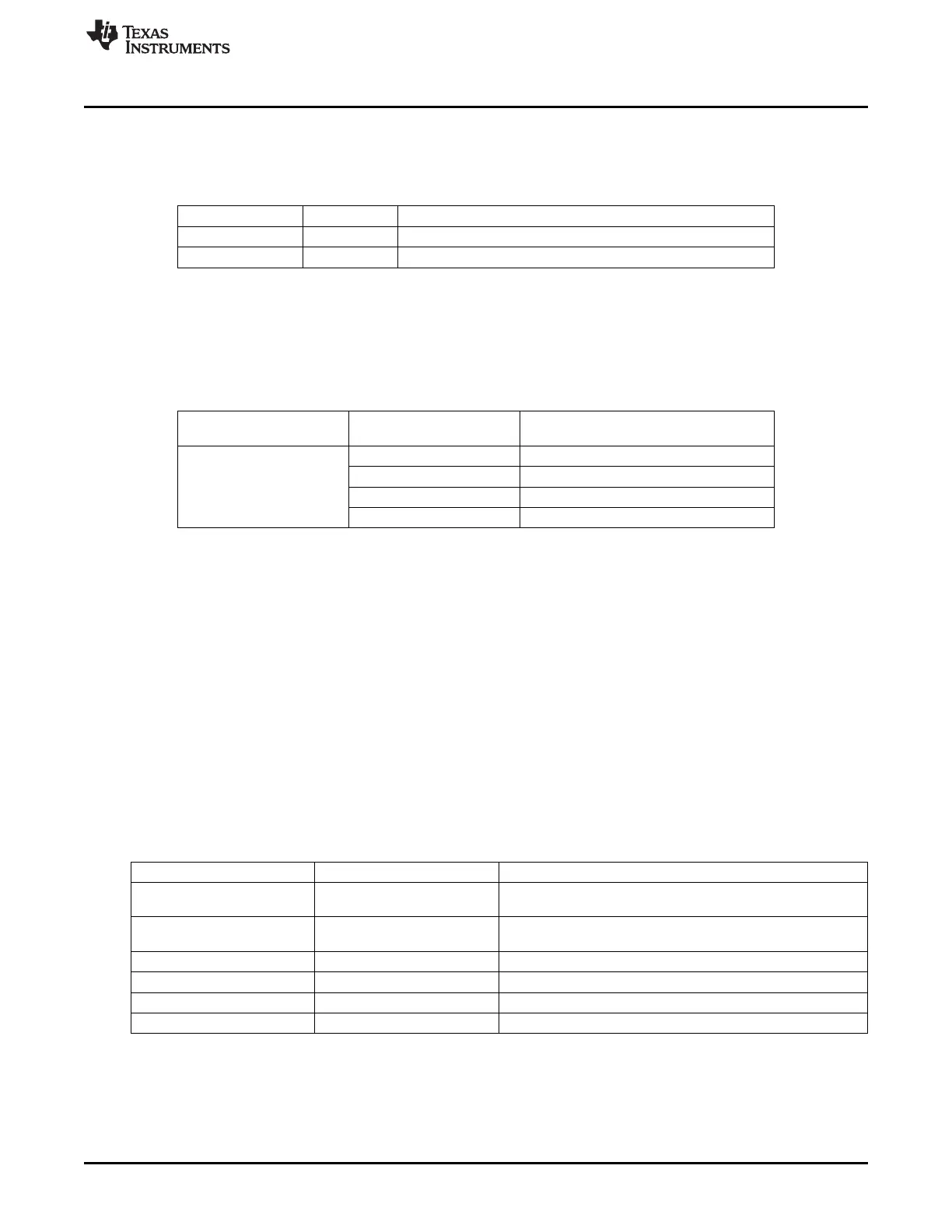

Table 7-7. GPMC_CONFIG1_i Configuration

GPMC_CONFIG1_i[1-0] GPMC_CLK Generated Clock

Source Clock

GPMCFCLKDIVIDER Provided to External Memory Device

00 GPMC_FCLK

01 GPMC_FCLK/2

GPMC_FCLK

10 GPMC_FCLK/3

11 GPMC_FCLK/4

7.1.3.3.2 GPMC Software Reset

The GPMC can be reset by software through the GPMC_SYSCONFIG[1] SOFTRESET bit. Setting the bit

to 1 enables an active software reset that is functionally equivalent to a hardware reset. Hardware and

software resets initialize all GPMC registers and the finite state-machine (FSM) immediately and

unconditionally. The GPMC_SYSSTATUS[0] RESETDONE bit indicates that the software reset is

complete when its value is 1. The software must ensure that the software reset completes before doing

GPMC operations.

7.1.3.3.3 GPMC Power Management

GPMC power is supplied by the CORE power domain, and GPMC power management complies with

system power-management guidelines. Table 7-8 describes power-management features available for the

GPMC module.

Table 7-8. GPMC Local Power Management Features

Feature Registers Description

GPMC_SYSCONFIG[0] This bit allows a local power optimization inside the module, by

Clock Auto Gating

AUTOIDLE] bit gating the GPMC_FCLK clock upon the internal activity.

GPMC_SYSCONFIG[4-3]

Slave Idle Modes Force-idle, No-idle and Smart-idle wakeup modes are available

SIDLEMODE bit field

Clock Activity N/A Feature not available

Master Standby Modes N/A Feature not available

Global Wake-up Enable N/A Feature not available

Wake-up Sources Enable N/A Feature not available

261

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...