Multimedia Card Registers

www.ti.com

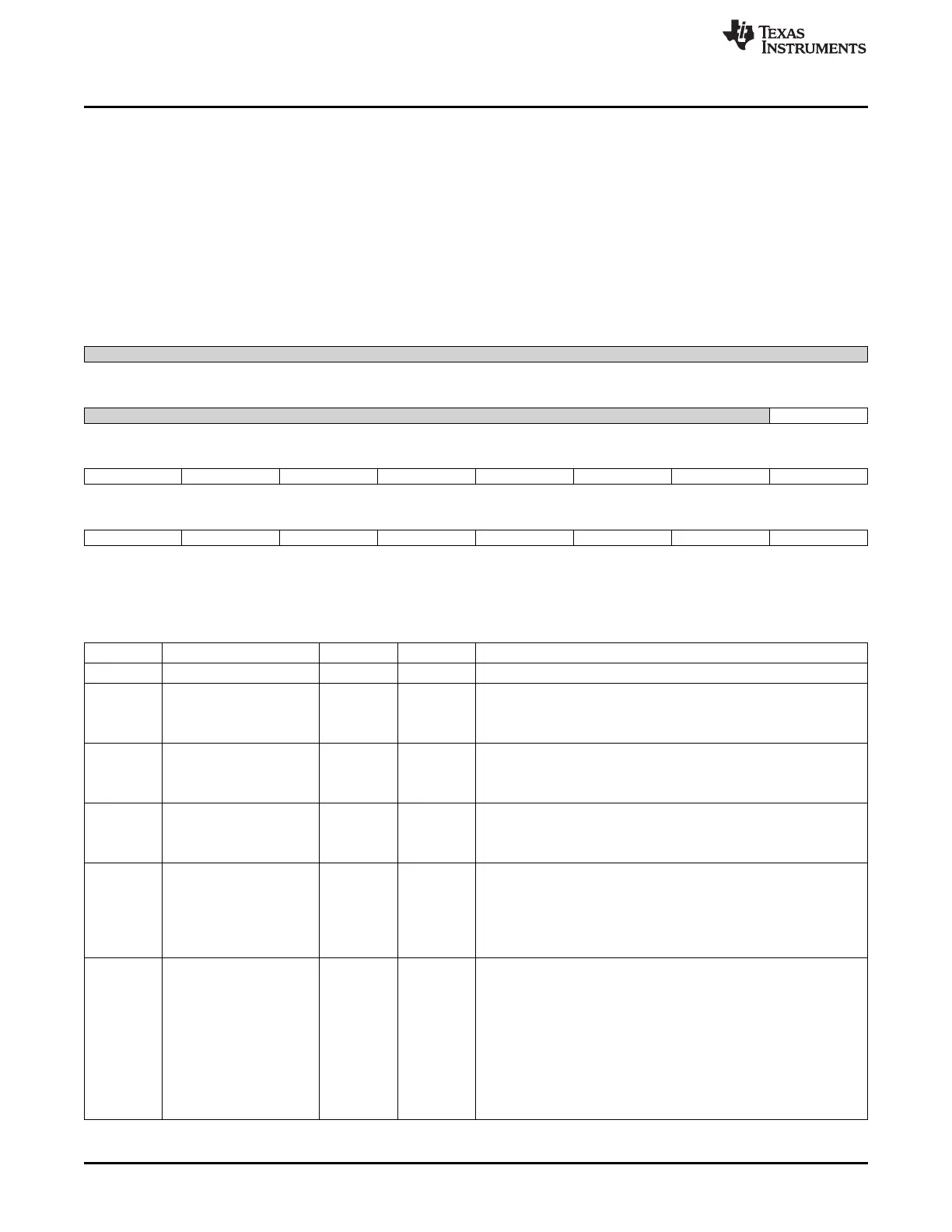

18.5.1.4 SD_SYSTEST Register (offset = 128h) [reset = 0h]

SD_SYSTEST is shown in Figure 18-40 and described in Table 18-23.

This register is used to control the signals that connect to I/O pins when the module is configured in

system test (SYSTEST) mode for boundary connectivity verification. In SYSTEST mode, a write into

SD_CMD register will not start a transfer. The buffer behaves as a stack accessible only by the local host

(push and pop operations). In this mode, the Transfer Block Size (SD_BLK[10:0] BLEN bits) and the

Blocks count for current transfer (SD_BLK[31:16] NBLK bits) are needed to generate a Buffer write ready

interrupt (SD_STAT[4] BWR bit) or a Buffer read ready interrupt (SD_STAT[5] BRR bit) and DMA requests

if enabled.

Figure 18-40. SD_SYSTEST Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved OBI

R-0h R/W-0h

15 14 13 12 11 10 9 8

SDCD SDWP WAKD SSB D7D D6D D5D D4D

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

D3D D2D D1D D0D DDIR CDAT CDIR MCKD

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

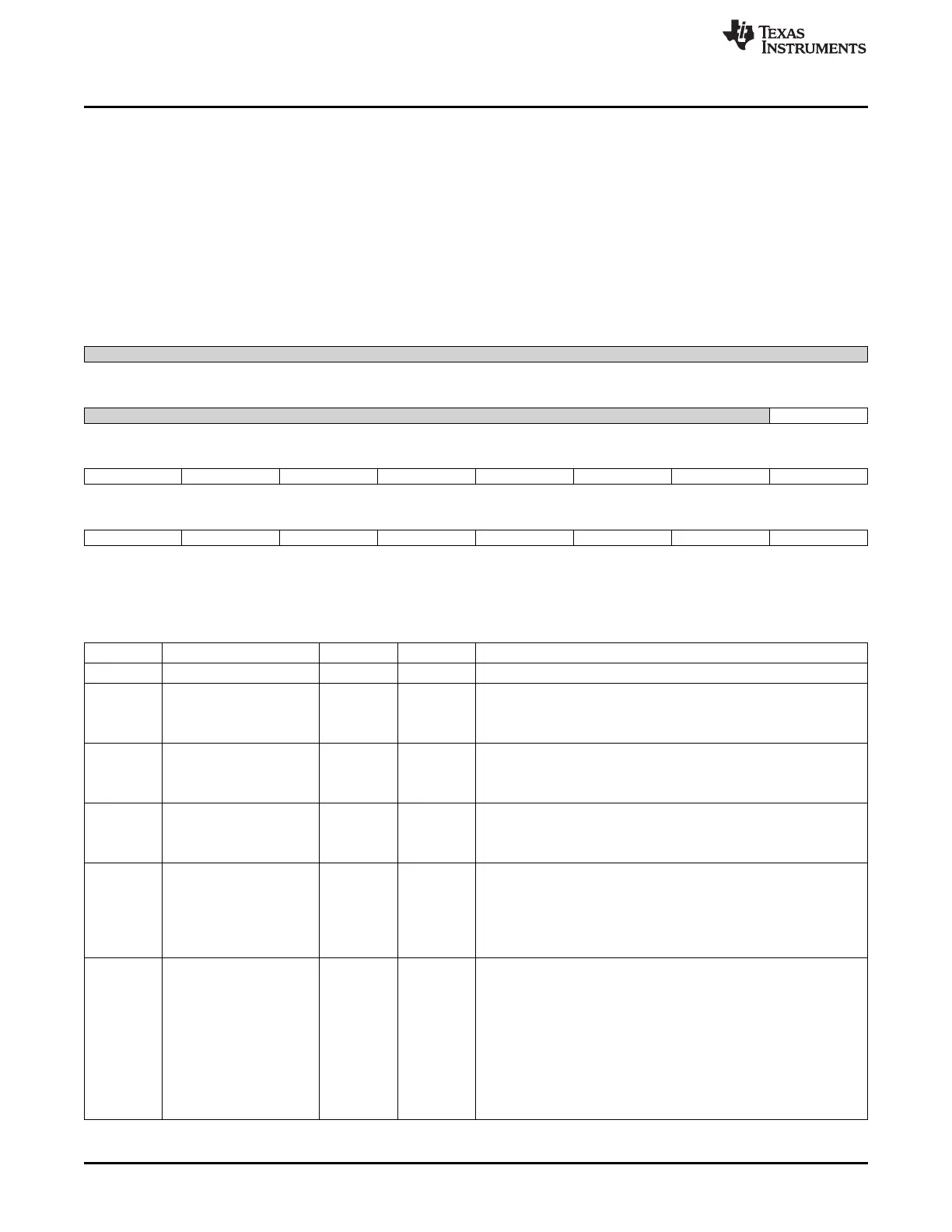

Table 18-23. SD_SYSTEST Register Field Descriptions

Bit Field Type Reset Description

31-17 Reserved R 0h

16 OBI R/W 0h

Out-of-band interrupt (OBI) data value.

0x0 = The out-of-band interrupt pin is driven low.

0x1 = The out-of-band interrupt pin is driven high.

15 SDCD R/W 0h

Card detect input signal (SDCD) data value

0x0 = The card detect pin is driven low.

0x1 = The card detect pin is driven high.

14 SDWP R/W 0h

Write protect input signal (SDWP) data value

0x0 = The write protect pin SDWP is driven low.

0x1 = The write protect pin SDWP is driven high.

13 WAKD R/W 0h

Wake request output signal data value.

0x0(W) = The pin SWAKEUP is driven low.

0x0(R) = No action. Returns 0.

0x1(W) = The pin SWAKEUP is driven high.

0x1(R) = No action. Returns 1.

12 SSB R/W 0h Set status bit.

This bit must be cleared prior attempting to clear a status bit of the

interrupt status register (SD_STAT).

0x0(W) = Clear this SSB bit field. Writing 0 does not clear already

set status bits.

0x0(R) = No action. Returns 0.

0x1(W) = Force to 1 all status bits of the interrupt status register

(SD_STAT) only if the corresponding bit field in the Interrupt signal

enable register (SD_ISE) is set.

0x1(R) = No action. Returns 1.

3394

Multimedia Card (MMC) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...