www.ti.com

GPMC

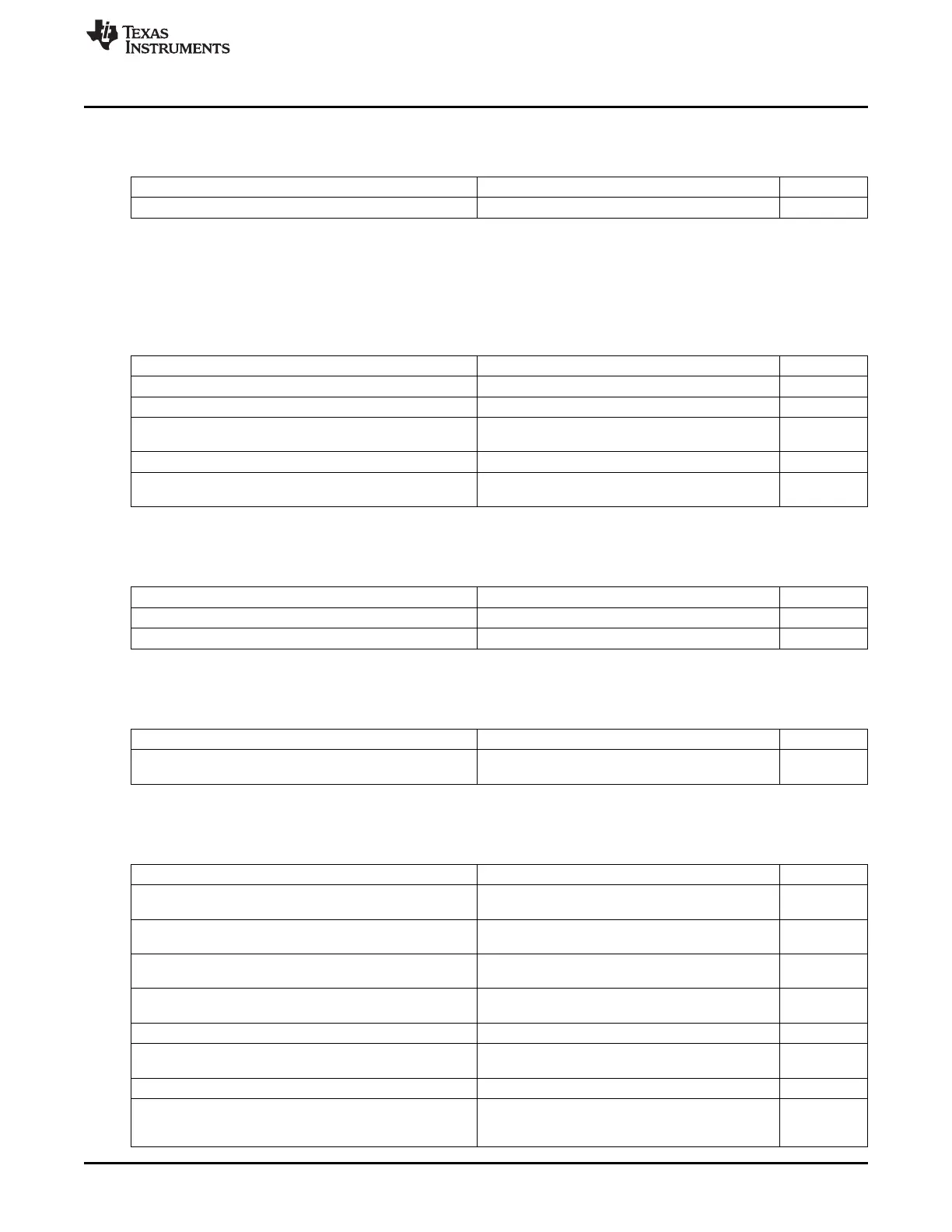

Table 7-31. Enable Chip-Select

Sub-process Name Register / Bitfield Value

When all parameters are configured, enable the chip-select GPMC_CONFIG7_i[6] CSVALID x

7.1.3.7 GPMC Configuration in NAND Mode

This section gives a generic configuration for parameters related to NAND memory connected to the

GPMC.

Table 7-32. NAND Memory Type

Sub-process Name Register / Bitfield Value

Set the NAND protocol GPMC_CONFIG1_i[11-10] DEVICETYPE 2h

Set a device size GPMC_CONFIG1_i[13-12] DEVICESIZE x

Set the address and data multiplexing protocol to non-

GPMC_CONFIG1_i[9] MUXADDDATA 0

multiplexed attached device

Select a timing signals latencies factor GPMC_CONFIG1_i[4] TIMEPARAGRANULARITY x

Set a synchronous or asynchronous mode and a single or

See Section 7.1.3.8 x

multiple access for read and write operations

Table 7-33. NAND Chip-Select Configuration

Sub-process Name Register / Bitfield Value

Select the chip-select base address GPMC_CONFIG7_i[5-0] BASEADDRESS x

Select the chip-select minimum granularity (16M bytes) GPMC_CONFIG7_i[11-8] MASKADDRESS x

Table 7-34. Asynchronous Read and Write Operations

Sub-process Name Register / Bitfield Value

Configure adequate timing parameters in asynchronous

See Section 7.1.3.9

modes

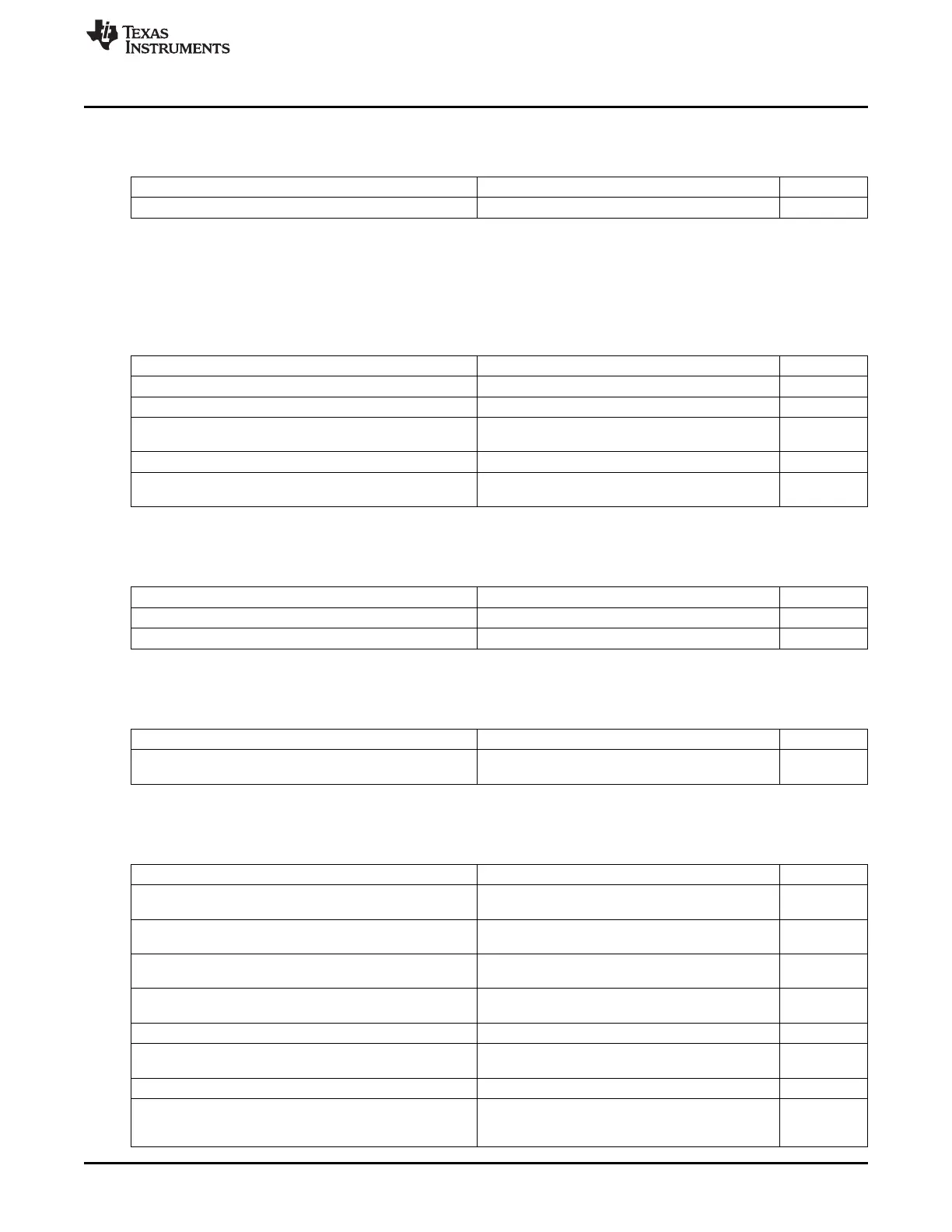

Table 7-35. ECC Engine

Sub-process Name Register / Bitfield Value

Select the ECC result register where the first ECC

GPMC_ECC_CONTROL[3-0] ECCPOINTER x

computation is stored (Only applies to Hamming)

Write 1 to

Clear all ECC result registers GPMC_ECC_CONTROL[8] ECCCLEAR

clear

GPMC_ECC_SIZE_CONFIG[19-12] ECCSIZE0 and

Define ECCSIZE0 and ECCSIZE1 x

GPMC_ECC_SIZE_CONFIG[29-22] ECCSIZE1

Select the size of each of the 9 result registers (size GPMC_ECC_SIZE_CONFIG[j-1] ECCjRESULTSIZE

x

specified by ECCSIZE0 or ECCSIZE1) where j = 1 to 9

Select the chip-select where ECC is computed GPMC_ECC_SIZE_CONFIG[3-1] ECCCS x

Select the Hamming code or BCH code ECC algorithm in

GPMC_ECC_SIZE_CONFIG[16] ECCALGORITHM x

use

Select word size for ECC calculation GPMC_ECC_SIZE_CONFIG[7] ECC16B x

If the BCH code is used, GPMC_ECC_SIZE_CONFIG[13-12] ECCBCHTSEL

Set an error correction capability and and GPMC_ECC_SIZE_CONFIG[6-4] x

Select a number of sectors to process ECCTOPSECTOR

339

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...