GPMC

www.ti.com

7.1.5.5 GPMC_IRQENABLE

The interrupt enable register allows to mask/unmask the module internal sources of interrupt, on a event-

by-event basis.

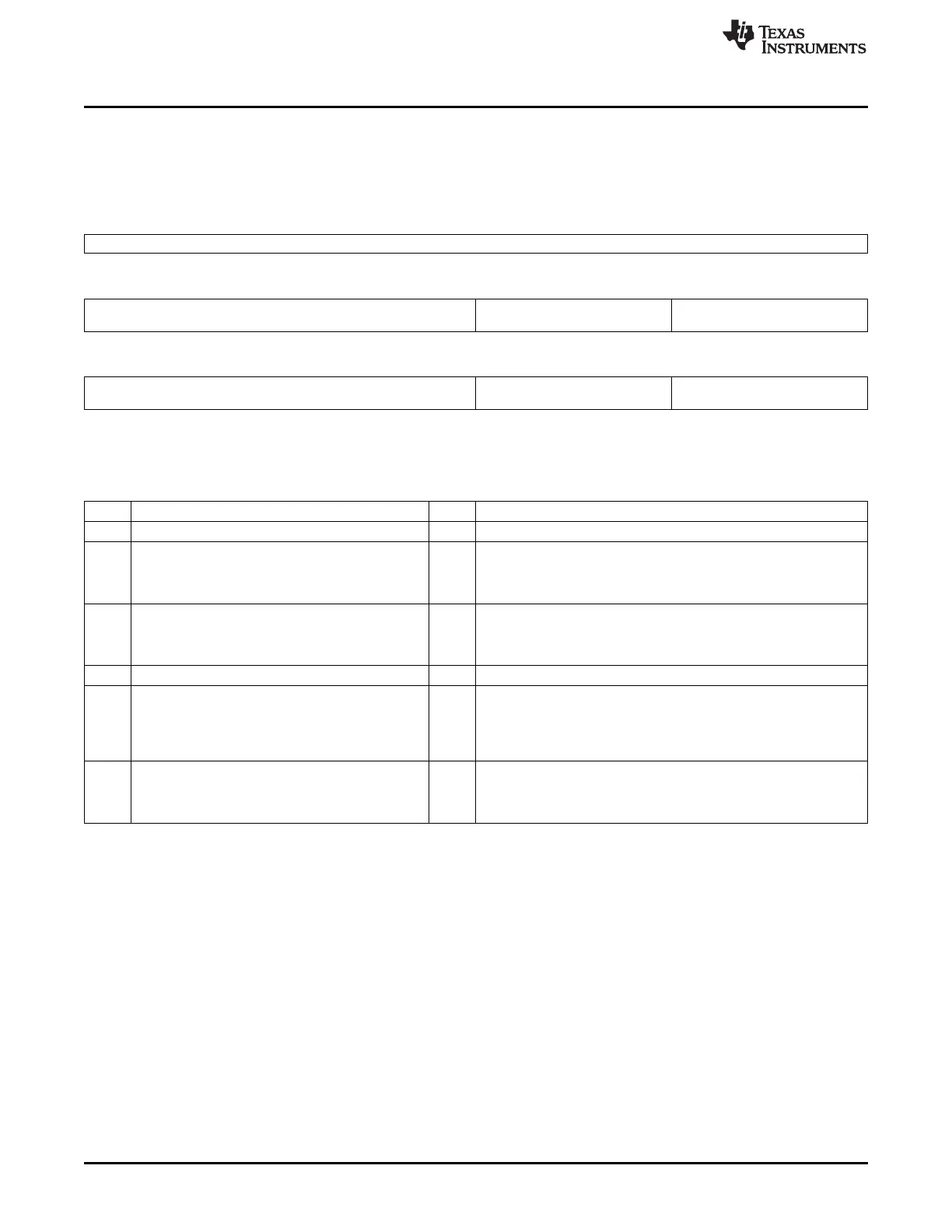

Figure 7-55. GPMC_IRQENABLE

31 16

Reserved

R-0

15 10 9 8

Reserved WAIT1EDGE WAIT0EDGE

DETECTIONENABLE DETECTIONENABLE

R-0 R/W-0 R/W-0

7 2 1 0

Reserved TERMINAL FIFOEVENT

COUNTENABLE ENABLE

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

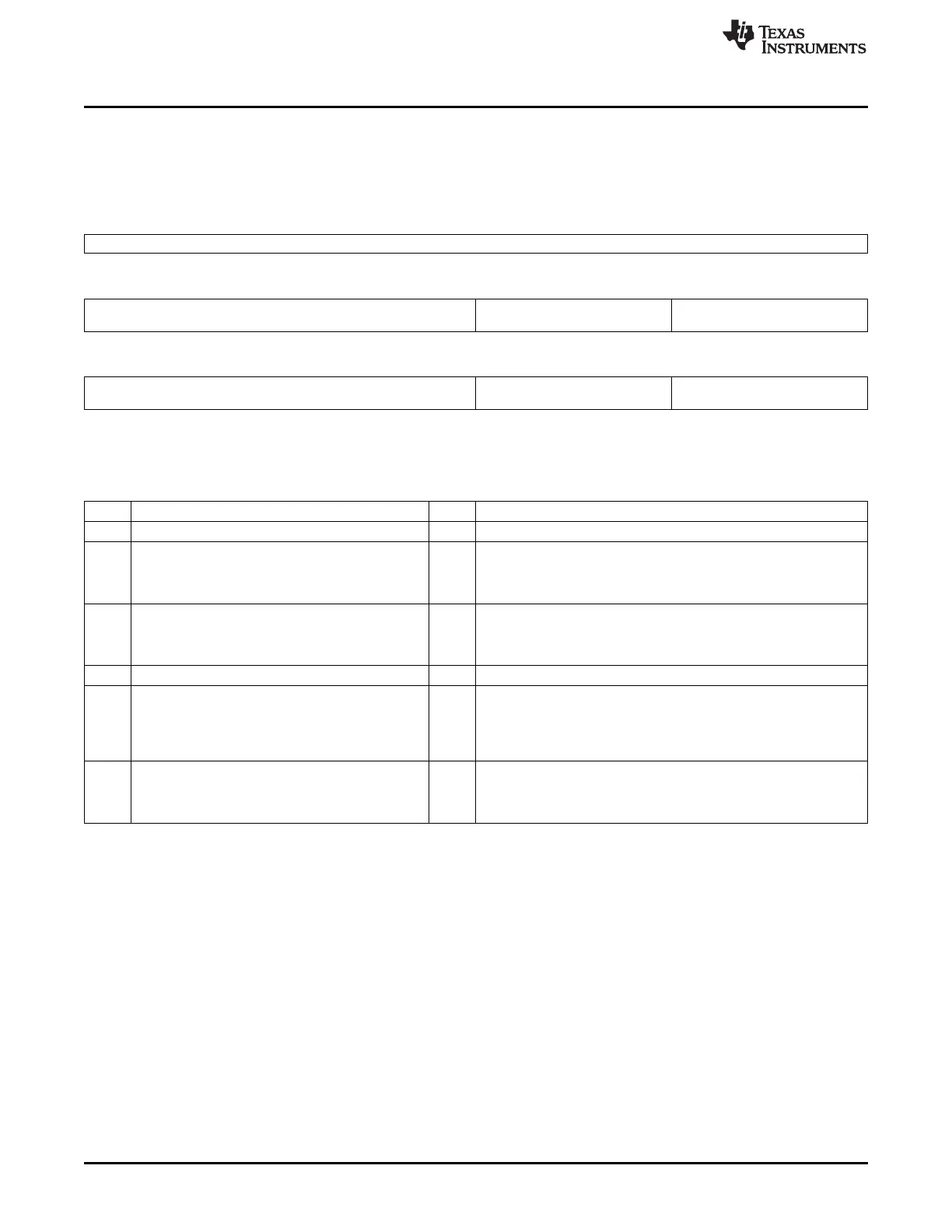

Table 7-59. GPMC_IRQENABLE Field Descriptions

Bit Field Value Description

31-10 Reserved 0 Reserved

9 WAIT1EDGEDETECTIONENABLE Enables the Wait1 Edge Detection interrupt

0 Wait1EdgeDetection interrupt is masked

1 Wait1EdgeDetection event generates an interrupt if occurs

8 WAIT0EDGEDETECTIONENABLE Enables the Wait0 Edge Detection interrupt

0 Wait0EdgeDetection interrupt is masked

1 Wait0EdgeDetection event generates an interrupt if occurs

7-2 Reserved 0 Reserved

1 TERMINALCOUNTEVENTENABLE Enables TerminalCountEvent interrupt issuing in pre-fetch or write

posting mode

0 TerminalCountEvent interrupt is masked

1 TerminalCountEvent interrupt is not masked

0 FIFOEVENTENABLE Enables the FIFOEvent interrupt

0 FIFOEvent interrupt is masked

1 FIFOEvent interrupt is not masked

370

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...