EDMA3 Registers

www.ti.com

11.4.1.5.2 Memory Protection Fault Status Register (MPFSR)

The memory protection fault status register (MPFSR) is shown in Figure 11-67 and described in Table 11-

51. A CPU write of 1 to the MPFCLR bit in the memory protection fault command register (MPFCR)

causes any error conditions stored in MPFSR to be cleared.

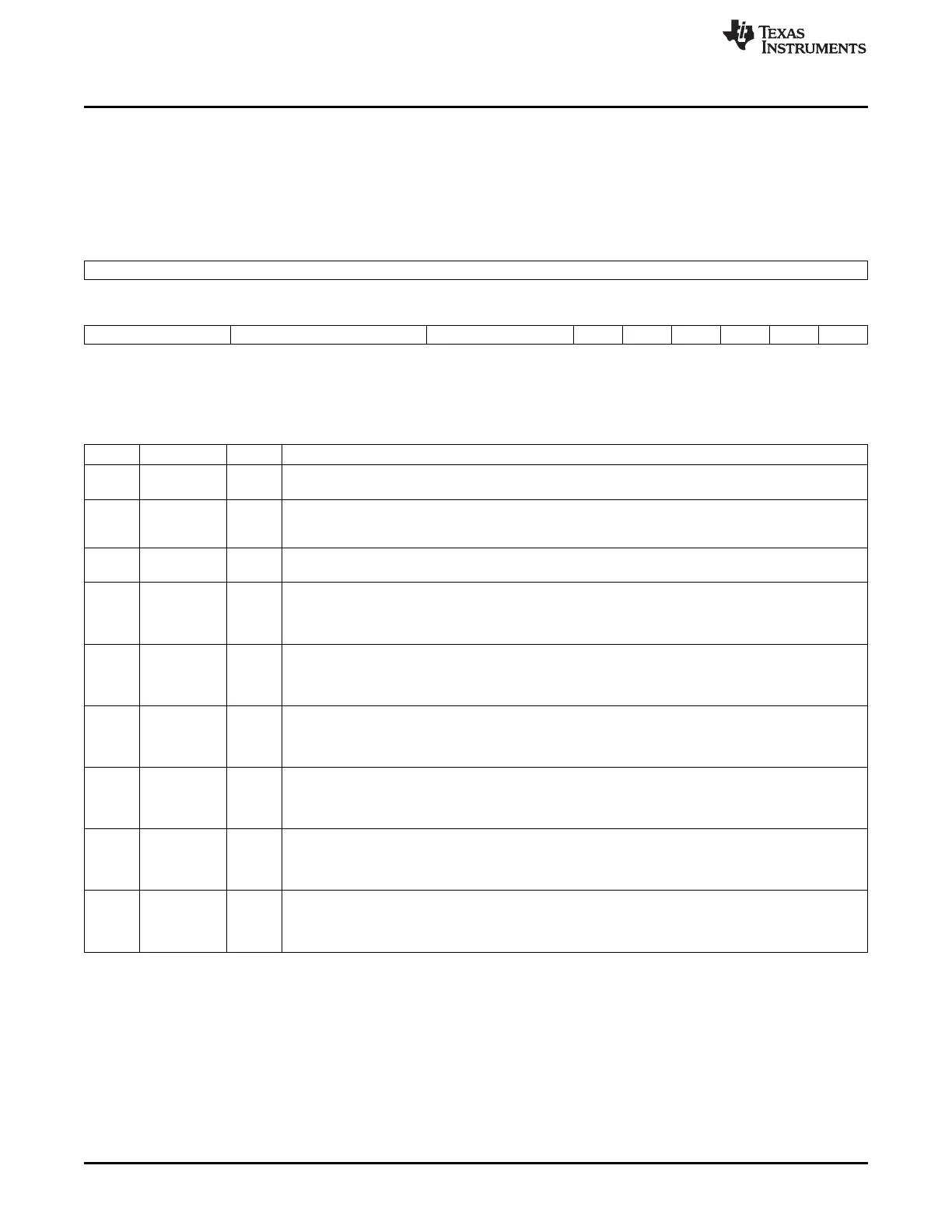

Figure 11-67. Memory Protection Fault Status Register (MPFSR)

31 16

Reserved

R-0

15 13 12 9 8 6 5 4 3 2 1 0

Reserved FID Reserved SRE SWE SXE URE UWE UXE

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

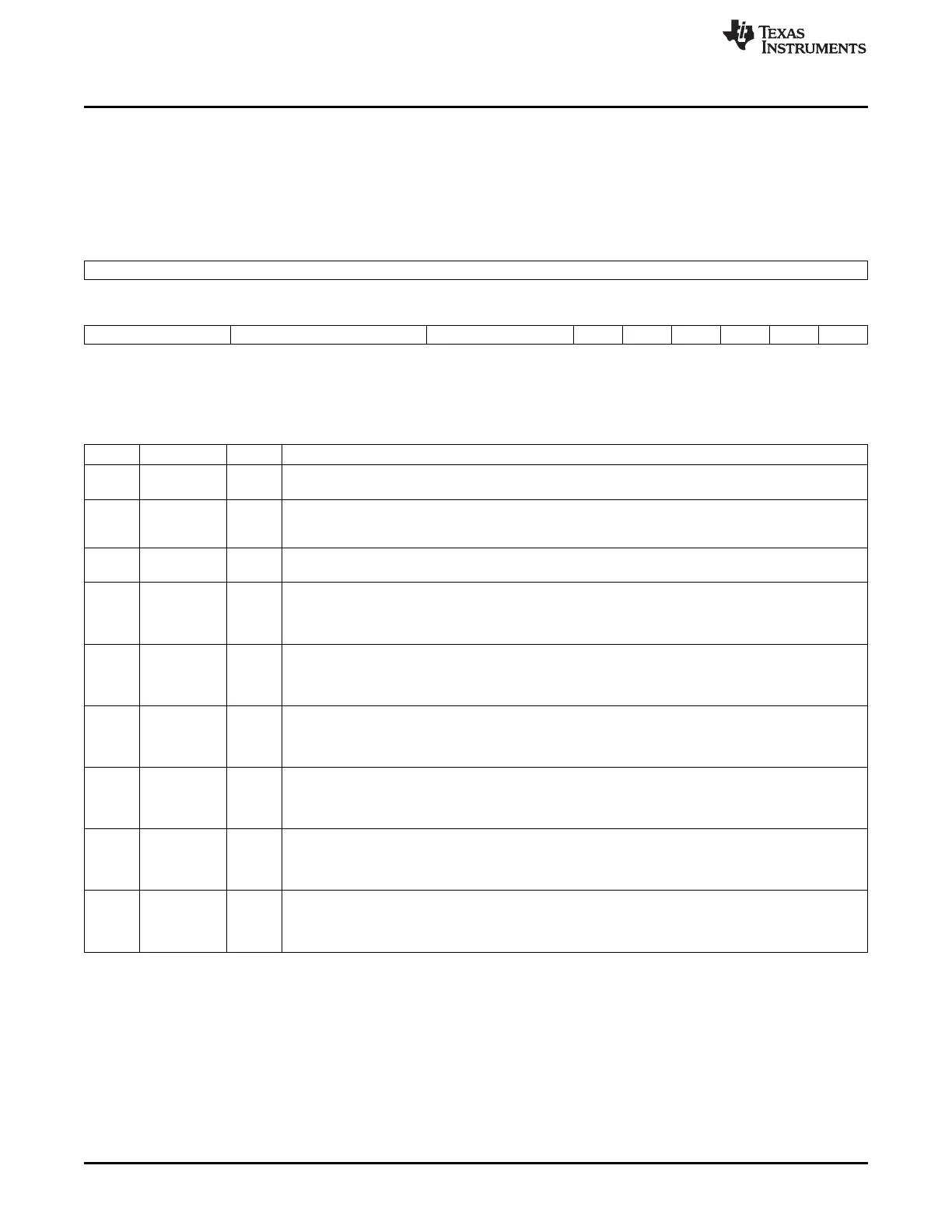

Table 11-51. Memory Protection Fault Status Register (MPFSR) Field Descriptions

Bit Field Value Description

31-13 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

12-9 FID 0-Fh Faulted identification. FID contains valid information if any of the MP error bits (UXE, UWE, URE, SXE,

SWE, SRE) are nonzero (that is, if an error has been detected.) The FID field contains the privilege ID

for the specific request/requestor that resulted in an MP error.

8-6 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

5 SRE Supervisor read error.

0 No error detected.

1 Supervisor level task attempted to read from a MP page without SR permissions.

4 SWE Supervisor write error.

0 No error detected.

1 Supervisor level task attempted to write to a MP page without SW permissions.

3 SXE Supervisor execute error.

0 No error detected.

1 Supervisor level task attempted to execute from a MP page without SX permissions.

2 URE User read error.

0 No error detected.

1 User level task attempted to read from a MP page without UR permissions.

1 UWE User write error.

0 No error detected.

1 User level task attempted to write to a MP page without UW permissions.

0 UXE User execute error.

0 No error detected.

1 User level task attempted to execute from a MP page without UX permissions.

966

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...