DCAN Registers

www.ti.com

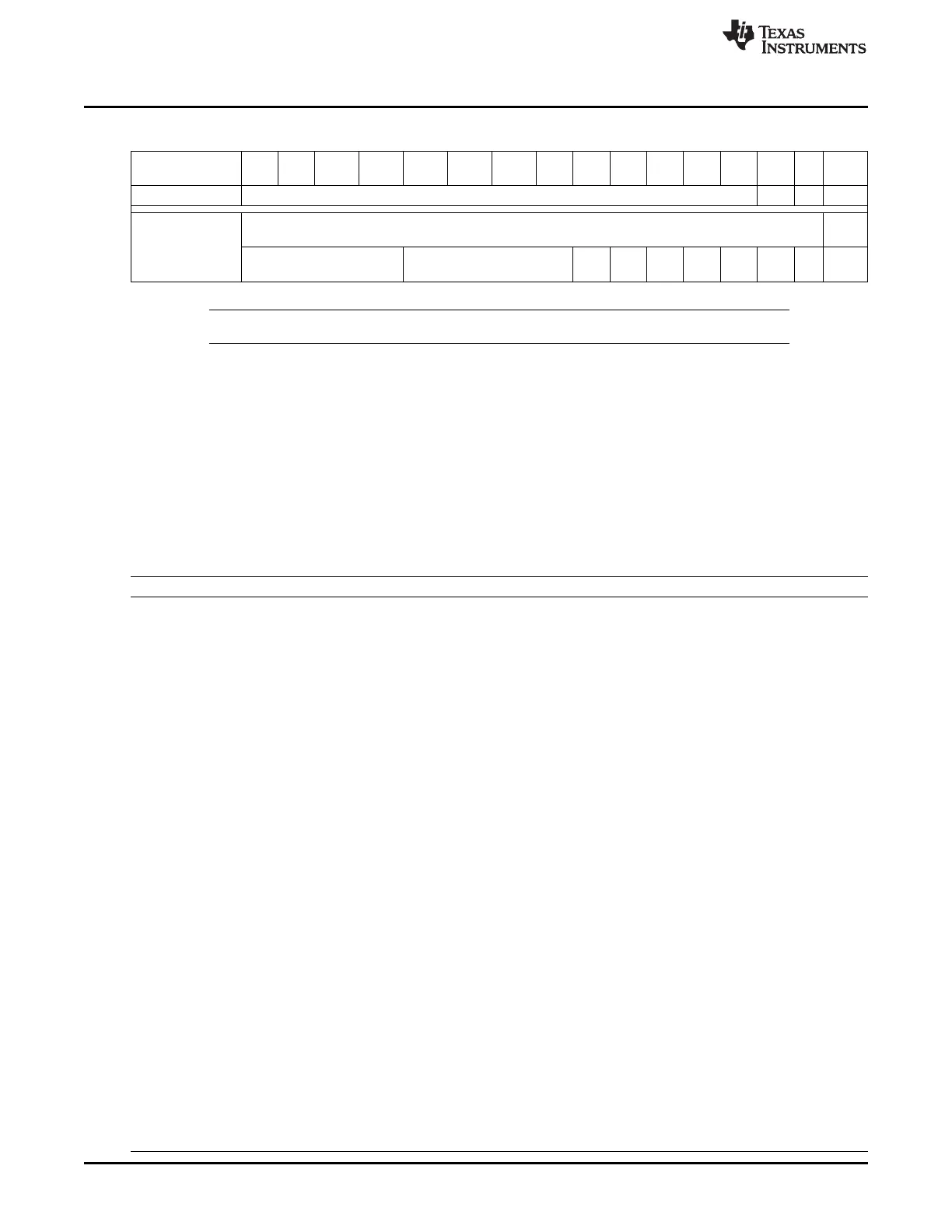

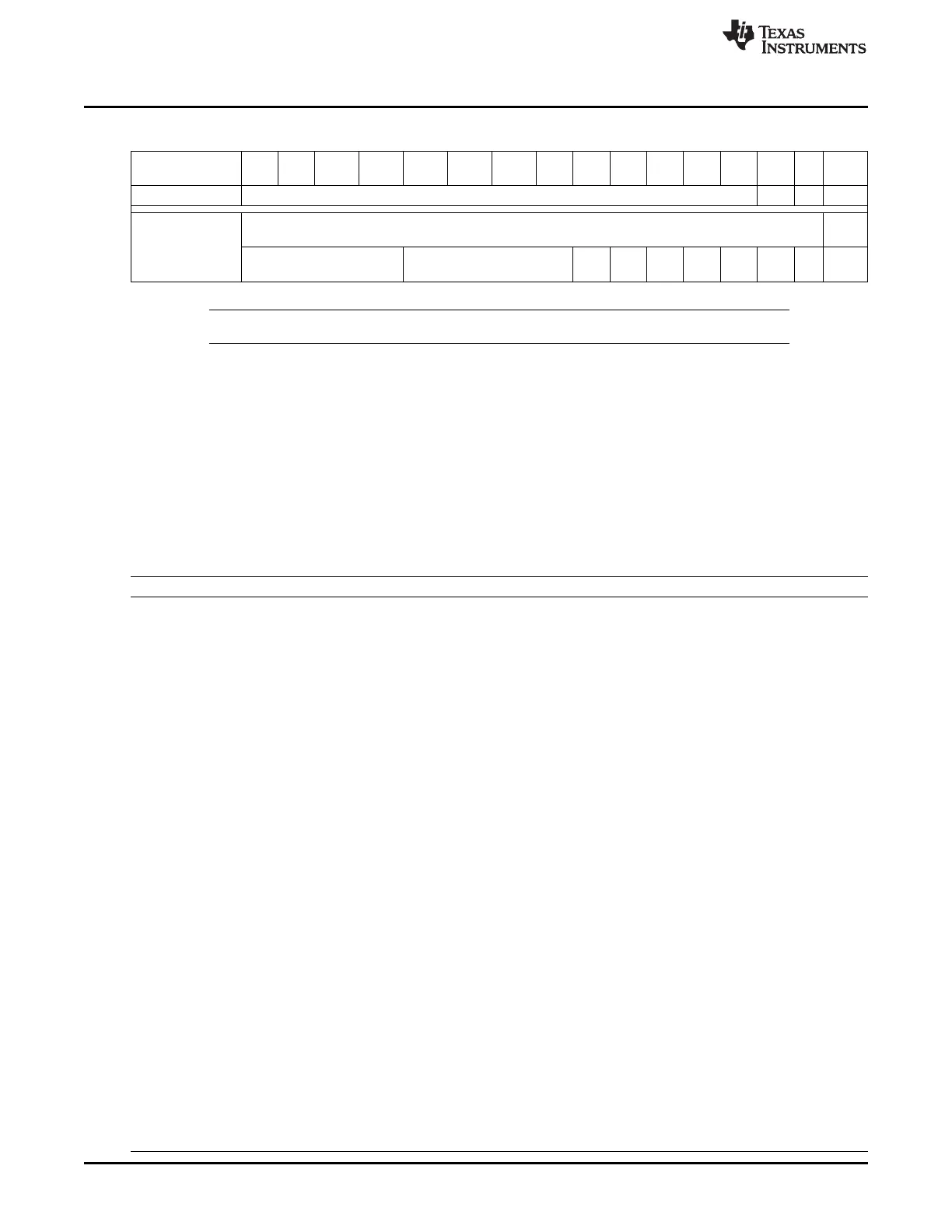

Table 23-12. Message RAM Representation in RAM Direct Access Mode (continued)

31/ 30/ 29/ 29/ 27/ 26/ 25/ 24/ 23/ 22/ 21/ 20/ 19/ 18/ 17/ 16/

Bit #

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

MsgAddr + 0x0C Msk[12:0] Xtd Dir ID[28]

Parity

Reserved

[4]

Msg UMa RxT Rmt MX

MsgAddr + 0x10 MsgLst Unused TxIE EOB MDir

Lst sk E En td

NOTE: Writes to unused bits have no effect.

23.3.19 GIO Support

The CAN_RX and CAN_TX pins of the DCAN module can be used as general purpose IO pins, if CAN

functionality is not needed. This function is controlled by the CAN TX IO control register (DCAN TIOC)

(see ) and the CAN RX IO control register (DCAN RIOC) (see ).

23.4 DCAN Registers

Table 23-13 lists the memory-mapped registers for the DCAN. All register offset addresses not listed in

Table 23-13 should be considered as reserved locations and the register contents should not be modified.

Table 23-13. DCAN REGISTERS

Offset Acronym Register Name Section

00h CTL CAN Control Register Section 23.4.1

04h ES Error and Status Register Section 23.4.2

08h ERRC Error Counter Register Section 23.4.3

0Ch BTR Bit Timing Register Section 23.4.4

10h INT Interrupt Register Section 23.4.5

14h TEST Test Register Section 23.4.6

1Ch PERR Parity Error Code Register Section 23.4.7

80h ABOTR Auto-Bus-On Time Register Section 23.4.8

84h TXRQ_X Transmission Request X Register Section 23.4.9

88h TXRQ12 Transmission Request Register 12 Section 23.4.10

8Ch TXRQ34 Transmission Request Register 34 Section 23.4.11

90h TXRQ56 Transmission Request Register 56 Section 23.4.12

94h TXRQ78 Transmission Request Register 78 Section 23.4.13

98h NWDAT_X New Data X Register Section 23.4.14

9Ch NWDAT12 New Data Register 12 Section 23.4.15

A0h NWDAT34 New Data Register 34 Section 23.4.16

A4h NWDAT56 New Data Register 56 Section 23.4.17

A8h NWDAT78 New Data Register 78 Section 23.4.18

ACh INTPND_X Interrupt Pending X Register Section 23.4.19

B0h INTPND12 Interrupt Pending Register 12 Section 23.4.20

B4h INTPND34 Interrupt Pending Register 34 Section 23.4.21

B8h INTPND56 Interrupt Pending Register 56 Section 23.4.22

BCh INTPND78 Interrupt Pending Register 78 Section 23.4.23

C0h MSGVAL_X Message Valid X Register Section 23.4.24

C4h MSGVAL12 Message Valid Register 12 Section 23.4.25

C8h MSGVAL34 Message Valid Register 34 Section 23.4.26

CCh MSGVAL56 Message Valid Register 56 Section 23.4.27

3922

Controller Area Network (CAN) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...