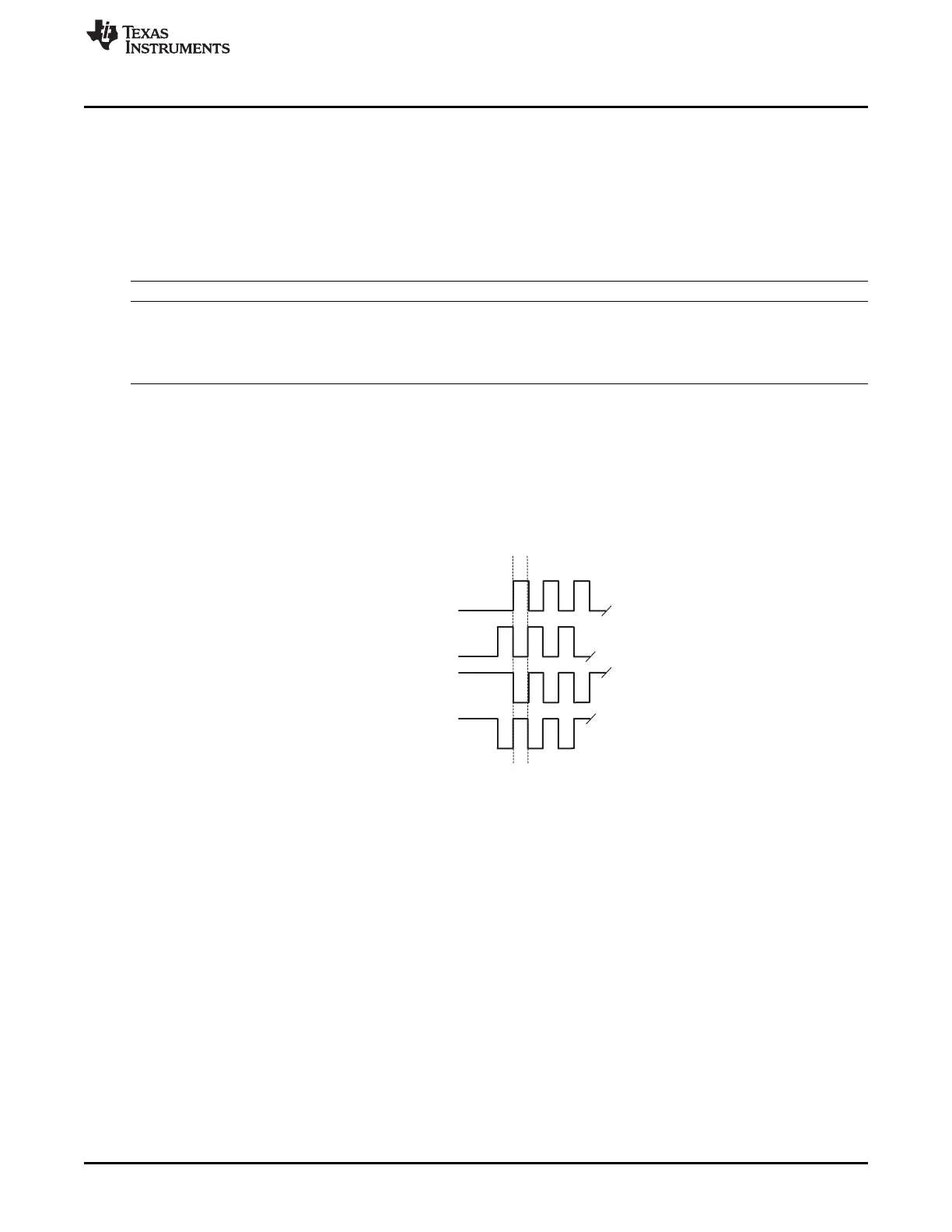

SPICLK (mode0)

Sampling

t

Lead

SPICLK (mode1)

SPICLK (mode2)

SPICLK (mode3)

www.ti.com

Functional Description

24.3.1.3.6 Polarity and Phase

McSPI supports four sub-modes of the SPI format transfer that depend on the polarity (POL) and the

phase (PHA) of the SPI serial clock (SPICLK). Table 24-5 and Figure 24-6 show a summary of the four

sub-modes. Software selects one of four combinations of serial clock phase and polarity.

Two consecutive SPI words for two different slave devices may go along with active SPICLK signal with

different phase and polarity.

Table 24-5. Phase and Polarity Combinations

Polarity (POL) Phase (PHA) SPI Mode Comments

0 0 mode0 SPICLK active high and sampling occurs on the rising edge.

0 1 mode1 SPICLK active high and sampling occurs on the falling edge.

1 0 mode2 SPICLK active low and sampling occurs on the falling edge.

1 1 mode3 SPICLK active low and sampling occurs on the rising edge.

Figure 24-6. Phase and Polarity Combinations

4001

SPRUH73H–October 2011–Revised April 2013 Multichannel Serial Port Interface (McSPI)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...