www.ti.com

UART Registers

19.5.1.29 BOF Length Register (EBLR)

In IrDA SIR operation, the BOF length register (EBLR) specifies the number of BOF + xBOFs to transmit.

The value set into this register must consider the BOF character; therefore, to send only one BOF with no

XBOF, this register must be set to 1. To send one BOF with n XBOFs, this register must be set to n + 1.

Furthermore, the value 0 sends 1 BOF plus 255 XBOFs.

In IrDA MIR mode, the BOF length register (EBLR) specifies the number of additional start flags (MIR

protocol mandates a minimum of 2 start flags).

In CIR mode, the BOF length register (EBLR) specifies the number of consecutive zeros to be received

before generating the RXSTOP interrupt (IIR[2]). All the received zeros are stored in the RX FIFO. When

the register is cleared to 0, this feature is deactivated and always in reception state, which is disabled by

setting the ACREG[5] bit to 1.

The BOF length register (EBLR) is shown in Figure 19-62 and described in Table 19-60.

NOTE: If the RX_STOP interrupt occurs before a byte boundary, the remaining bits of the last byte

are filled with zeros and then passed into the RX FIFO.

Figure 19-62. BOF Length Register (EBLR)

15 8 7 0

Reserved EBLR

R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

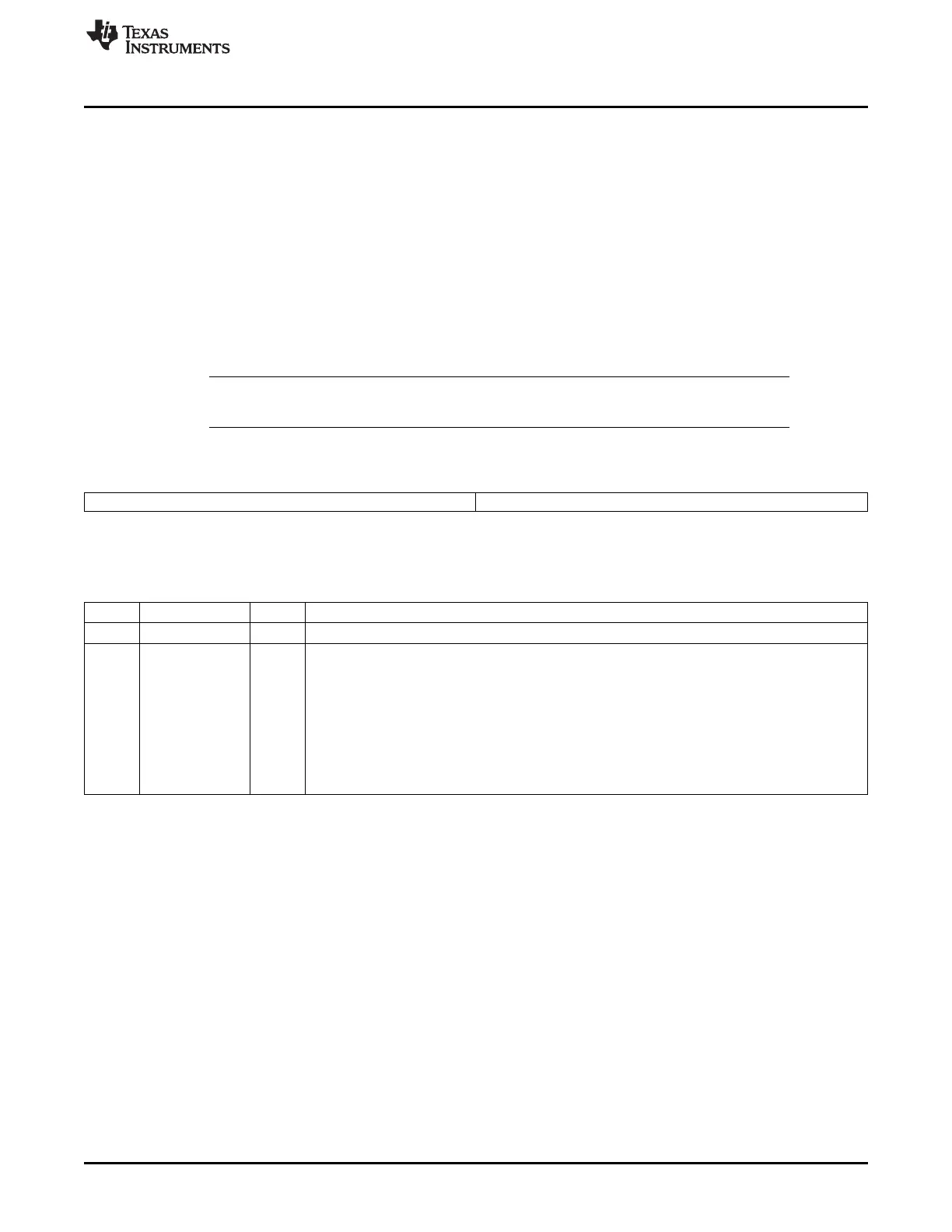

Table 19-60. BOF Length Register (EBLR) Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7-0 EBLR IrDA mode: This register allows definition of up to 176 xBOFs, the maximum required by IrDA

specification.

CIR mode: This register specifies the number of consecutive zeros to be received before

generating the RXSTOP interrupt (IIR[2]).

0 Feature disabled.

1h Generate RXSTOP interrupt after receiving 1 zero bit.

...

FFh Generate RXSTOP interrupt after receiving 255 zero bits.

3531

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...