www.ti.com

EMIF

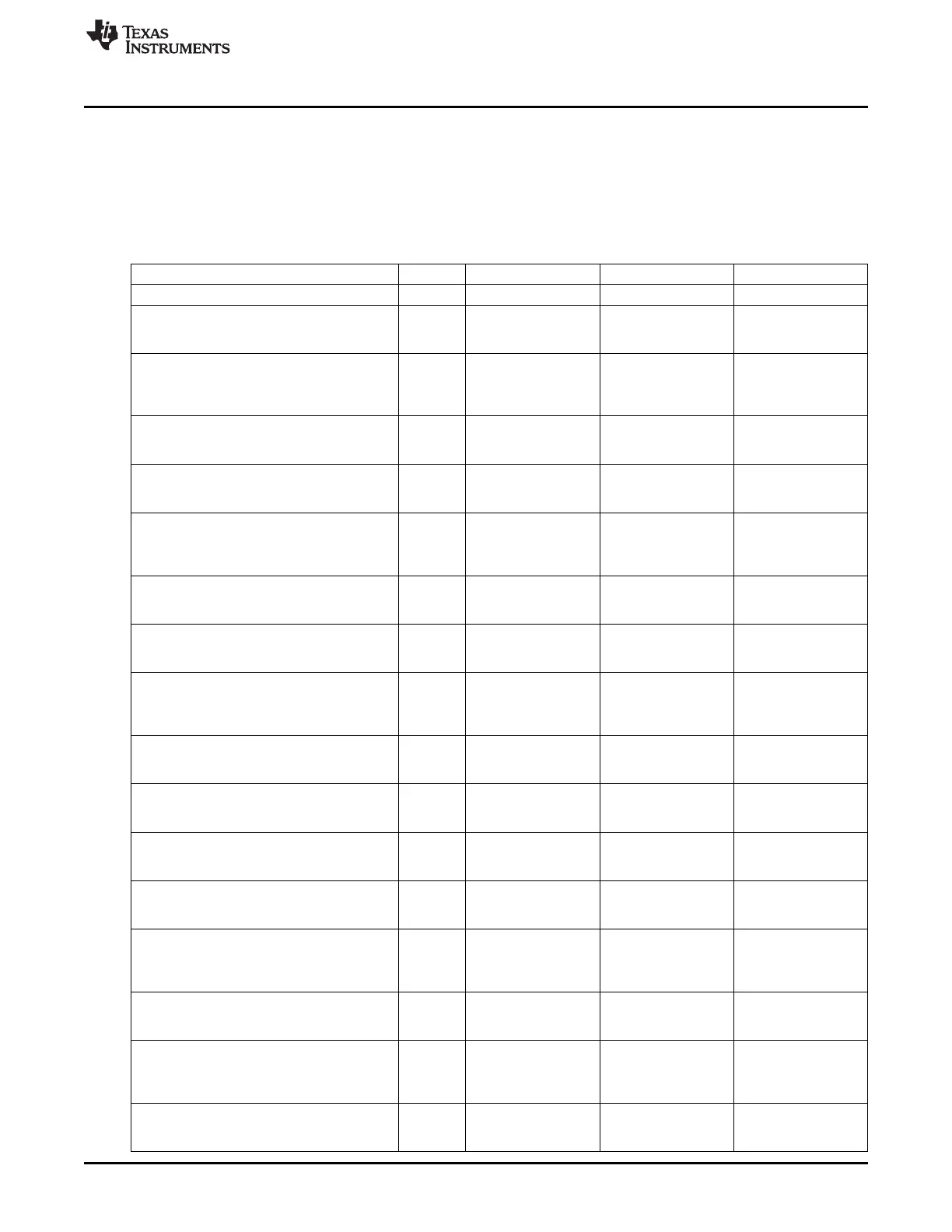

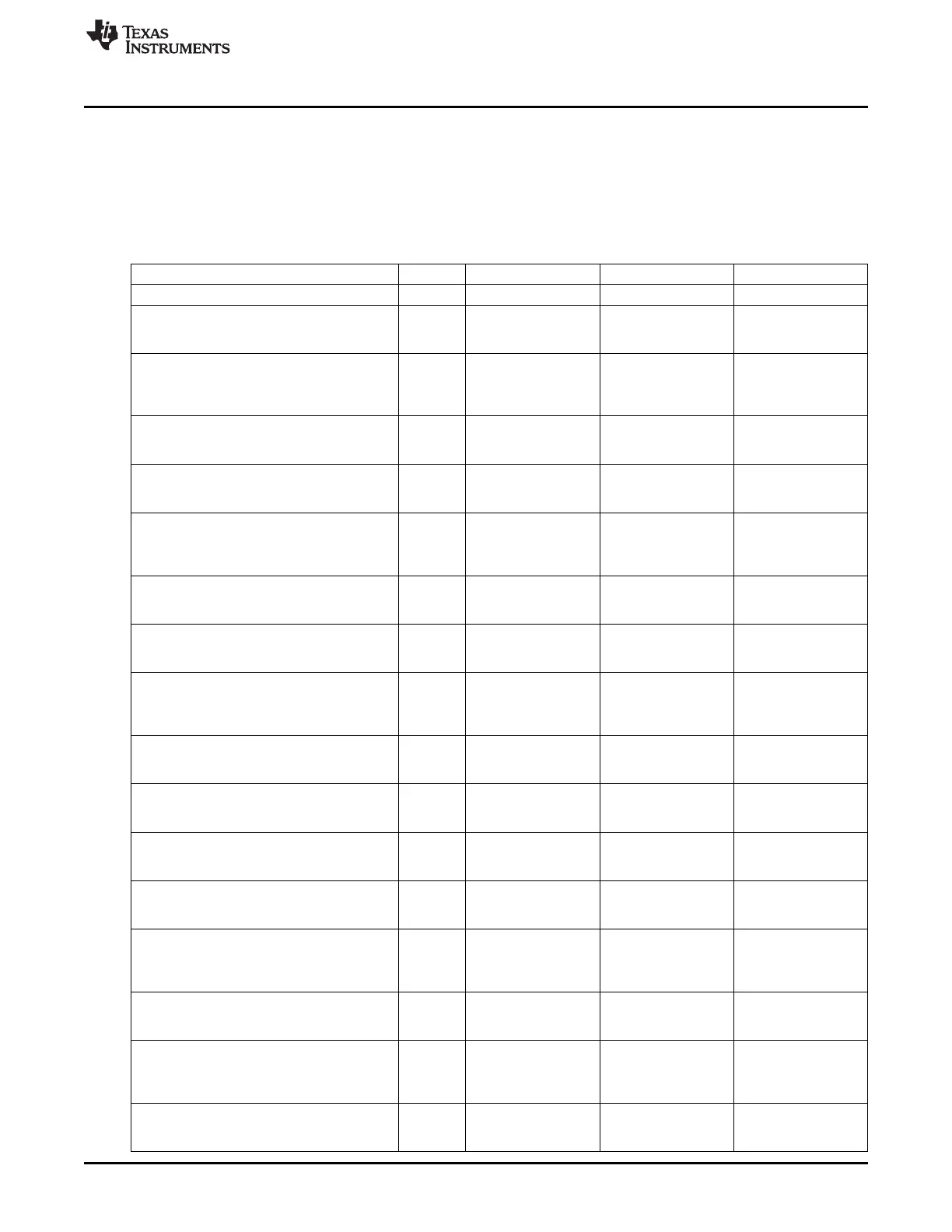

7.3.6 DDR2/3/mDDR PHY Registers

Table 7-149 lists the memory-mapped registers for the DDR2/3 mDDR PHY. Configure the DDR PHY

Control Register for calibration of board delay and other parameters to get the SDRAM device working at

a different speed.

Note: These registers are write-only due to a silicon bug. The contents of these registers cannot be read.

Table 7-149. Memory-Mapped Registers for DDR2/3/mDDR PHY

Register Name Type Register Register Address

Description Reset Offset

CMD0_REG_PHY_CTRL_SLAVE_RATIO_0 W DDR PHY Command 0x80 0x01C

0 Address/Command

Slave Ratio Register

CMD0_REG_PHY_DLL_LOCK_DIFF_0 W DDR PHY Command 0x4 0x028

0 Address/Command

DLL Lock Difference

Register

CMD0_REG_PHY_INVERT_CLKOUT_0 W DDR PHY Command 0x0 0x02C

0 Invert Clockout

Selection Register

CMD1_REG_PHY_CTRL_SLAVE_RATIO_0 W DDR PHY Command 0x80 0x050

1 Address/Command

Slave Ratio Register

CMD1_REG_PHY_DLL_LOCK_DIFF_0 W DDR PHY Command 0x4 0x05C

1 Address/Command

DLL Lock Difference

Register

CMD1_REG_PHY_INVERT_CLKOUT_0 W DDR PHY Command 0x0 0x060

1 Invert Clockout

Selection Register

CMD2_REG_PHY_CTRL_SLAVE_RATIO_0 W DDR PHY Command 0x80 0x084

2 Address/Command

Slave Ratio Register

CMD2_REG_PHY_DLL_LOCK_DIFF_0 W DDR PHY Command 0x4 0x090

2 Address/Command

DLL Lock Difference

Register

CMD2_REG_PHY_INVERT_CLKOUT_0 W DDR PHY Command 0x0 0x094

2 Invert Clockout

Selection Register

DATA0_REG_PHY_RD_DQS_SLAVE_RATIO W DDR PHY Data Macro 0x04010040 0x0C8

_0 0 Read DQS Slave

Ratio Register

DATA0_REG_PHY_WR_DQS_SLAVE_RATI W DDR PHY Data Macro 0x0 0x0DC

O_0 0 Write DQS Slave

Ratio Register

DATA0_REG_PHY_WRLVL_INIT_RATIO_0 W DDR PHY Data Macro 0x0 0x0F0

0 Write Leveling Init

Ratio Register

DATA0_REG_PHY_WRLVL_INIT_MODE_0 W DDR PHY Data Macro 0x0 0x0F8

0 Write Leveling Init

Mode Ratio Selection

Register

DATA0_REG_PHY_GATELVL_INIT_RATIO_0 W DDR PHY Data Macro 0x0 0x0FC

0 DQS Gate Training

Init Ratio Register

DATA0_REG_PHY_GATELVL_INIT_MODE_0 W DDR PHY Data Macro 0x0 0x104

0 DQS Gate Training

Init Mode Ratio

Selection Register

DATA0_REG_PHY_FIFO_WE_SLAVE_RATI W DDR PHY Data Macro 0x0 0x108

O_0 0 DQS Gate Slave

Ratio Register

467

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...