GPMC

www.ti.com

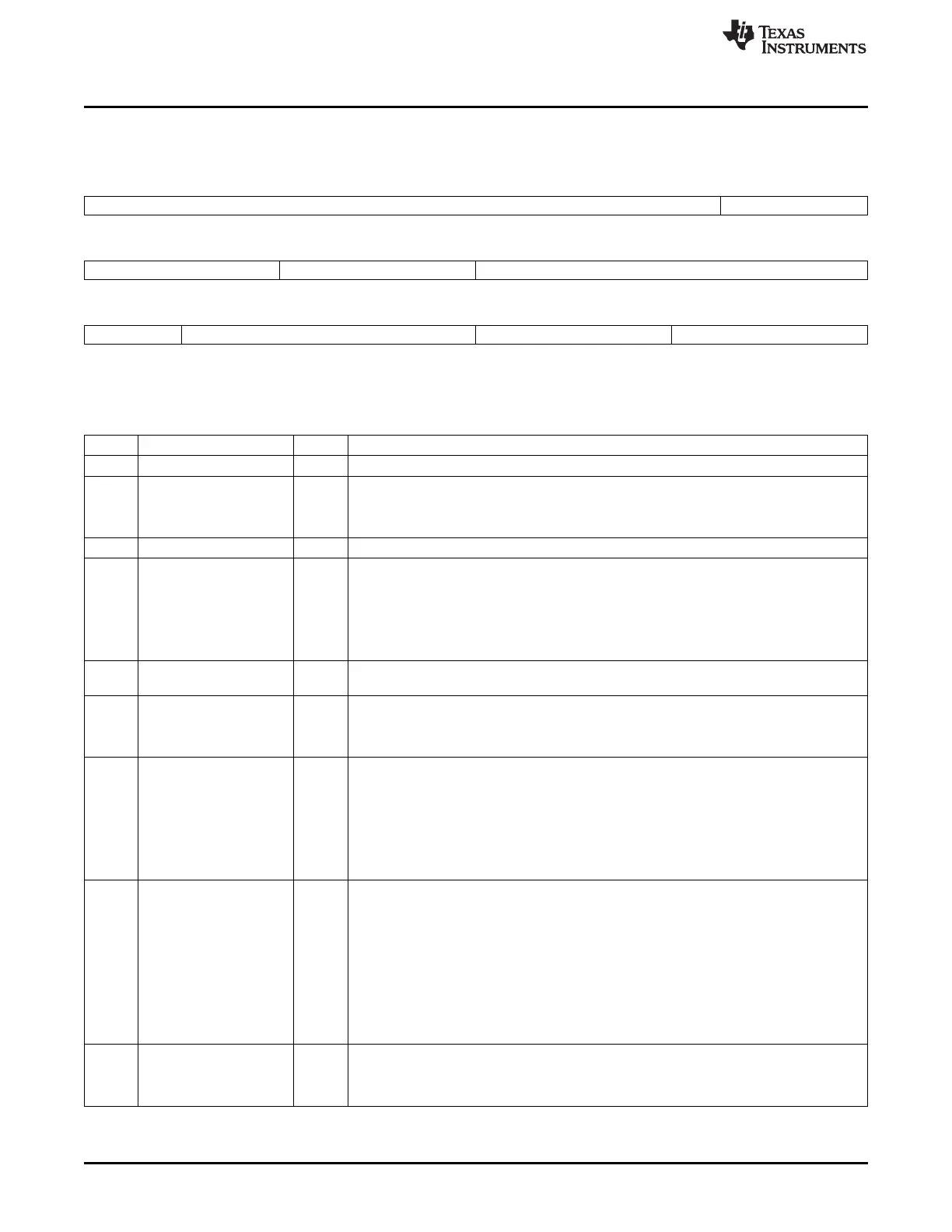

7.1.5.25 GPMC_ECC_CONFIG

Figure 7-75. GPMC_ECC_CONFIG

31 17 16

Reserved ECCALGORITHM

R-0 R/W-0

15 14 13 12 11 8

Reserved ECCBCHTSEL ECCWRAPMODE

R-0 R/W-0 R/W-0

7 6 4 3 1 0

ECC16B ECCTOPSECTOR ECCCS ECCENABLE

R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

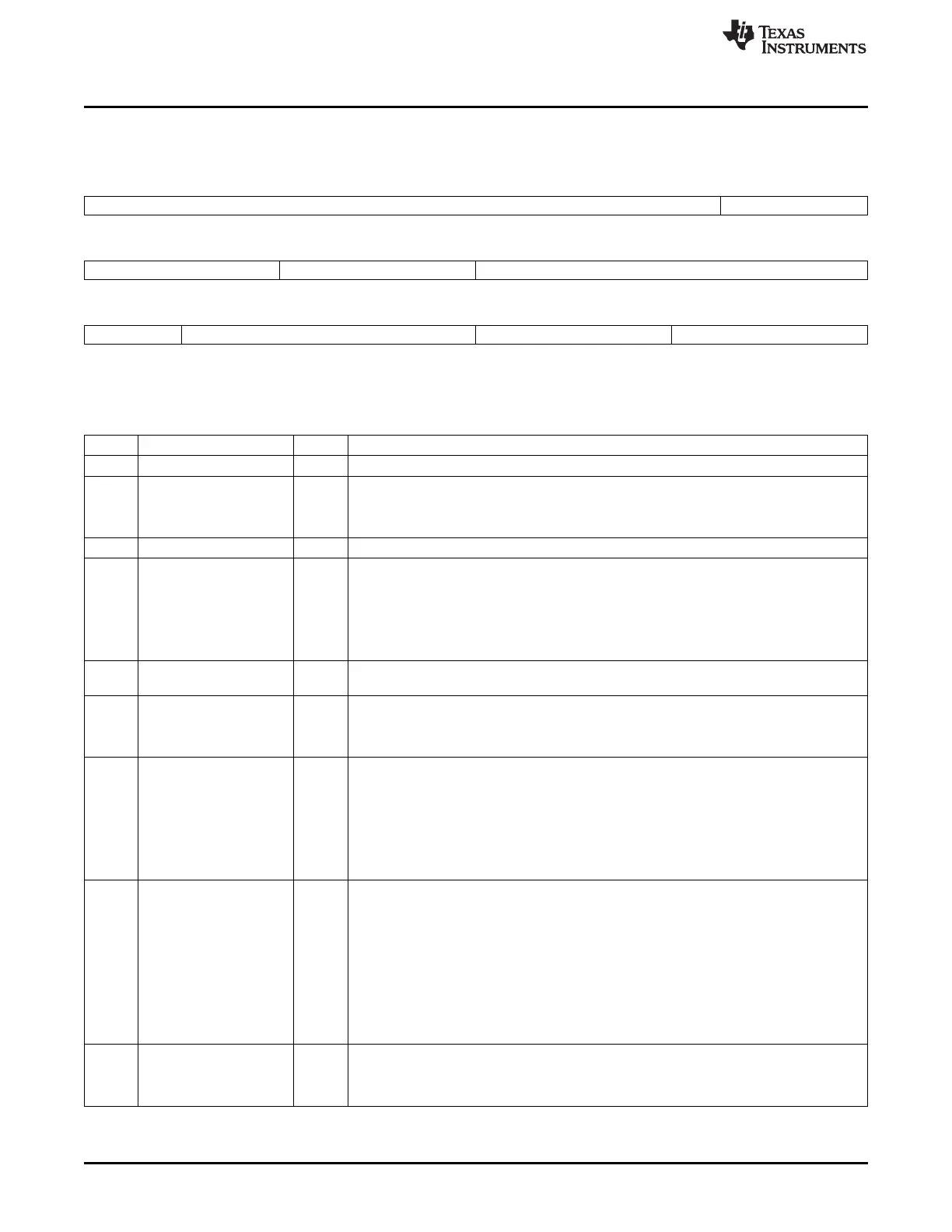

Table 7-79. GPMC_ECC_CONFIG Field Descriptions

Bit Field Value Description

31-17 Reserved 0 Reserved

16 ECCALGORITHM ECC algorithm used

0 Hamming code

1 BCH code

15-14 Reserved 0 Reserved

13-12 ECCBCHTSEL Error correction capability used for BCH

0 Up to 4 bits error correction (t = 4)

1h Up to 8 bits error correction (t = 8)

2h Up to 16 bits error correction (t = 16)

3h Reserved

11-8 ECCWRAPMODE 0-Fh Spare area organization definition for the BCH algorithm. See the BCH syndrome/parity

calculator module functional specification for more details

7 ECC16B Selects an ECC calculated on 16 columns

0 ECC calculated on 8 columns

1 ECC calculated on 16 columns

6-4 ECCTOPSECTOR Number of sectors to process with the BCH algorithm

0 1 sector (512kB page)

1h 2 sectors

3h 4 sectors (2kB page)

⋮ ⋮

7h 8 sectors (4kB page)

3-1 ECCCS Selects the Chip-select where ECC is computed

0 Chip-select 0

1h Chip-select 1

2h Chip-select 2

3h Chip-select 3

4h Chip-select 4

5h Chip-select 5

6h-7h Reserved

0 ECCENABLE Enables the ECC feature

0 ECC disabled

1 ECC enabled

390

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...