UART Registers

www.ti.com

19.5.1.52 Mode Definition Register 3 (MDR3) Register

The DISABLE_CIR_RX_DEMOD register bit will force the CIR receiver to bypass demodulation of

received data if set. See the CIR Mode Block Components. The NONDEFAULT_FREQ register bit allows

the user to set sample per bit by writing it into FREQ_SEL register. Set it if non-default (48 MHz) fclk

frequency is used to achieve a less than 2% error rate. Changing this bit (to any value) will automatically

disable the device by setting MDR[2:0] to “111”.

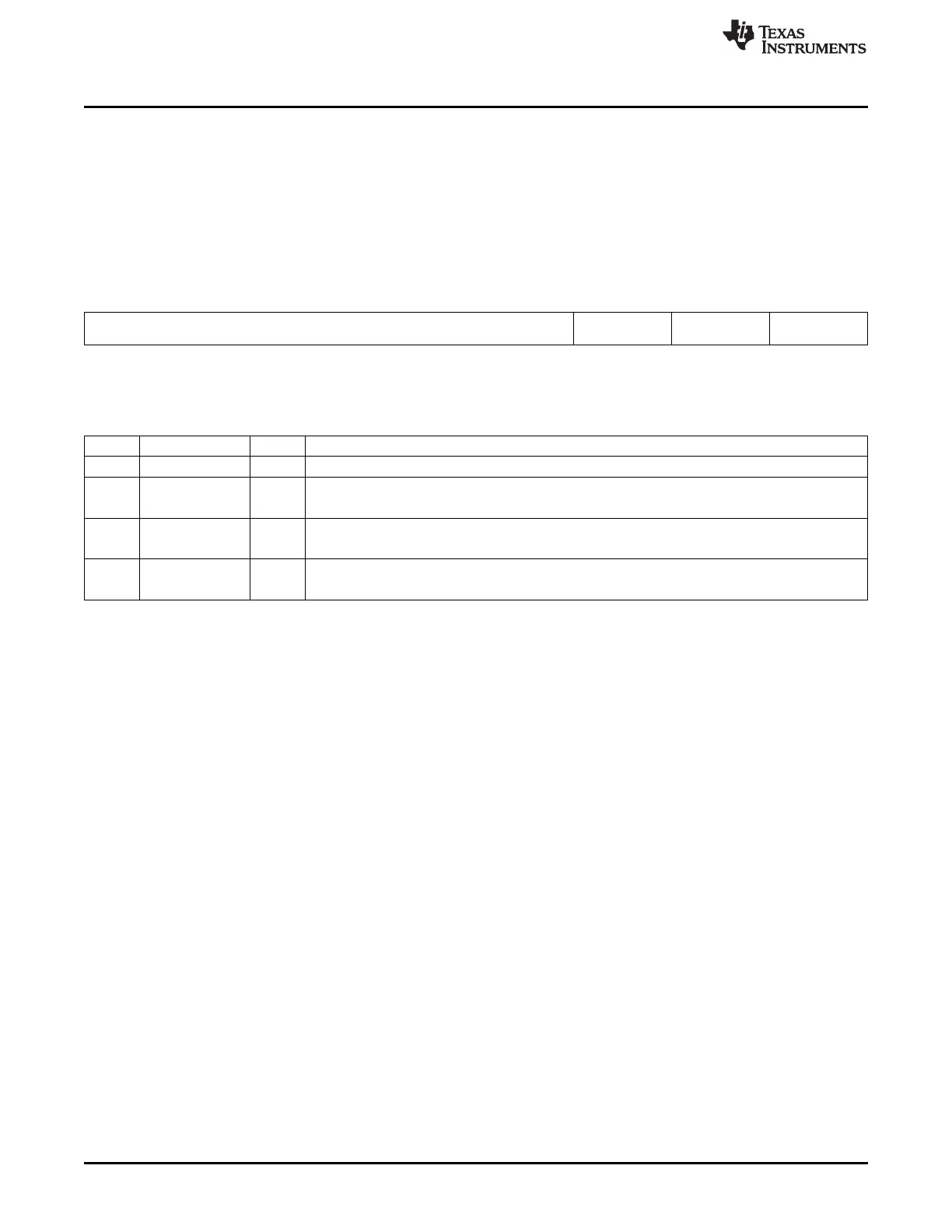

The Mode Definition Register 3 (MDR3) register is shown in Figure 19-79 and described in Table 19-78.

Figure 19-85. Mode Definition Register 3 (MDR3) Register

31 3 2 1 0

Reserved SET_DMA_TX_ NONDEFAULT DISABLE_CIR_

THRESHOLD _FREQ RX_DEMOD

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

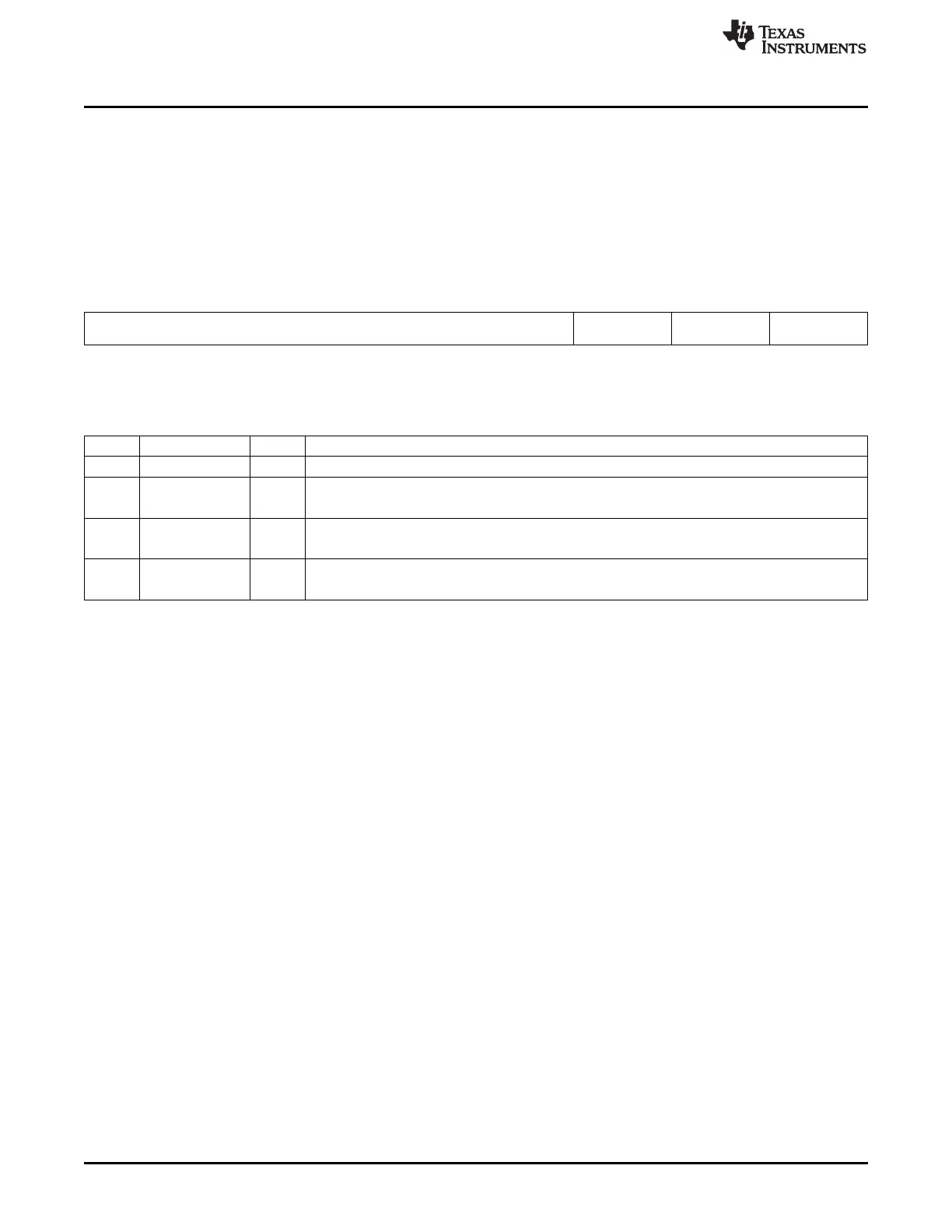

Table 19-84. Mode Definition Register 3 (MDR3) Register Field Descriptions

Bit Field Value Description

31-3 Reserved 0 Reserved.

2 SET_DMA_TX_T 0 Disable use of TX DMA Threshold register. Use 64-TX trigger as DMA threshold.

HRESHOLD

1 Enable to set different TX DMA threshold in the TX DMA Threshold register.

1 NONDEFAULT_F 0 Disables using NONDEFAULT fclk frequencies

REQ

1 Enables using NONDEFAULT fclk frequencies (set FREQ_SEL and DLH/DLL)

0 DISABLE_CIR_R 0 Enables CIR RX demodulation

X_DEMOD

1 Disables CIR RX demodulation

3548

Universal Asynchronous Receiver/Transmitter (UART) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...