www.ti.com

EDMA3 Registers

11.4.1.7 Interrupt Registers

All DMA/QDMA channels can be set to assert an EDMA3CC completion interrupt to the CPU on transfer

completion, by appropriately configuring the PaRAM entry associated with the channels. The following set

of registers is used for the transfer completion interrupt reporting/generating by the EDMA3CC. For more

details on EDMA3CC completion interrupt generation, see EDMA3 Interrupts.

11.4.1.7.1 Interrupt Enable Registers (IER, IERH)

Interrupt enable registers (IER/IERH) are used to enable/disable the transfer completion interrupt

generation by the EDMA3CC for all DMA/QDMA channels. The IER/IERH cannot be written to directly. To

set any interrupt bit in IER/IERH, a 1 must be written to the corresponding interrupt bit in the interrupt

enable set registers (IESR/IESRH). Similarly, to clear any interrupt bit in IER/IERH, a 1 must be written to

the corresponding interrupt bit in the interrupt enable clear registers (IECR/IECRH).

The IER is shown in Figure 11-88 and described in Table 11-72. The IERH is shown in Figure 11-89 and

described in Table 11-73.

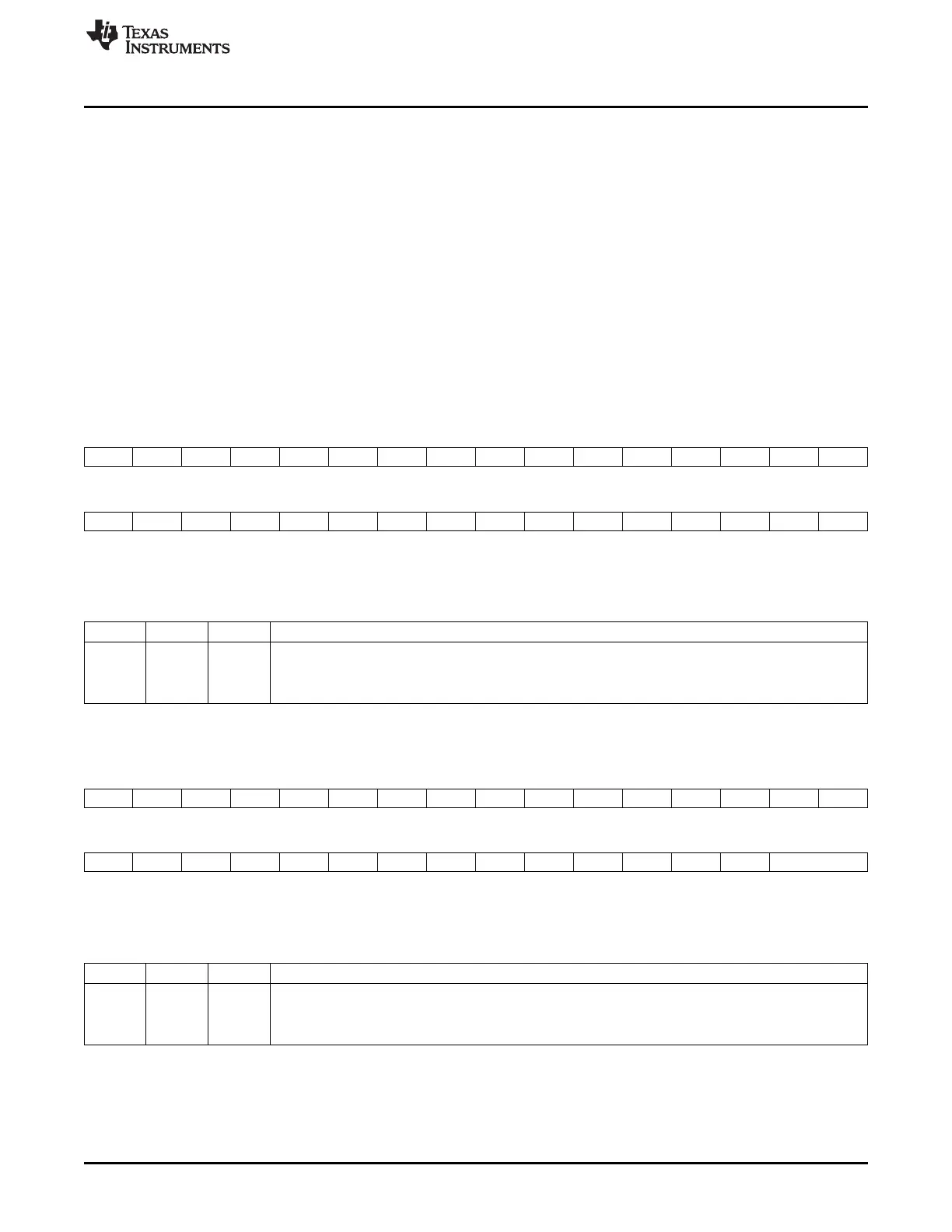

Figure 11-88. Interrupt Enable Register (IER)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

I31 I30 I29 I28 I27I I26 I25 I24 I23 I22 I21 I20 I19 I18 I17 I16

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

I15 I14 I13 I12 I11 I10 I9 I8 I7 I6 I5 I4 I3 I2 I1 I0

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 11-72. Interrupt Enable Register (IER) Field Descriptions

Bit Field Value Description

31-0 En Interrupt enable for channels 0-31.

0 Interrupt is not enabled.

1 Interrupt is enabled.

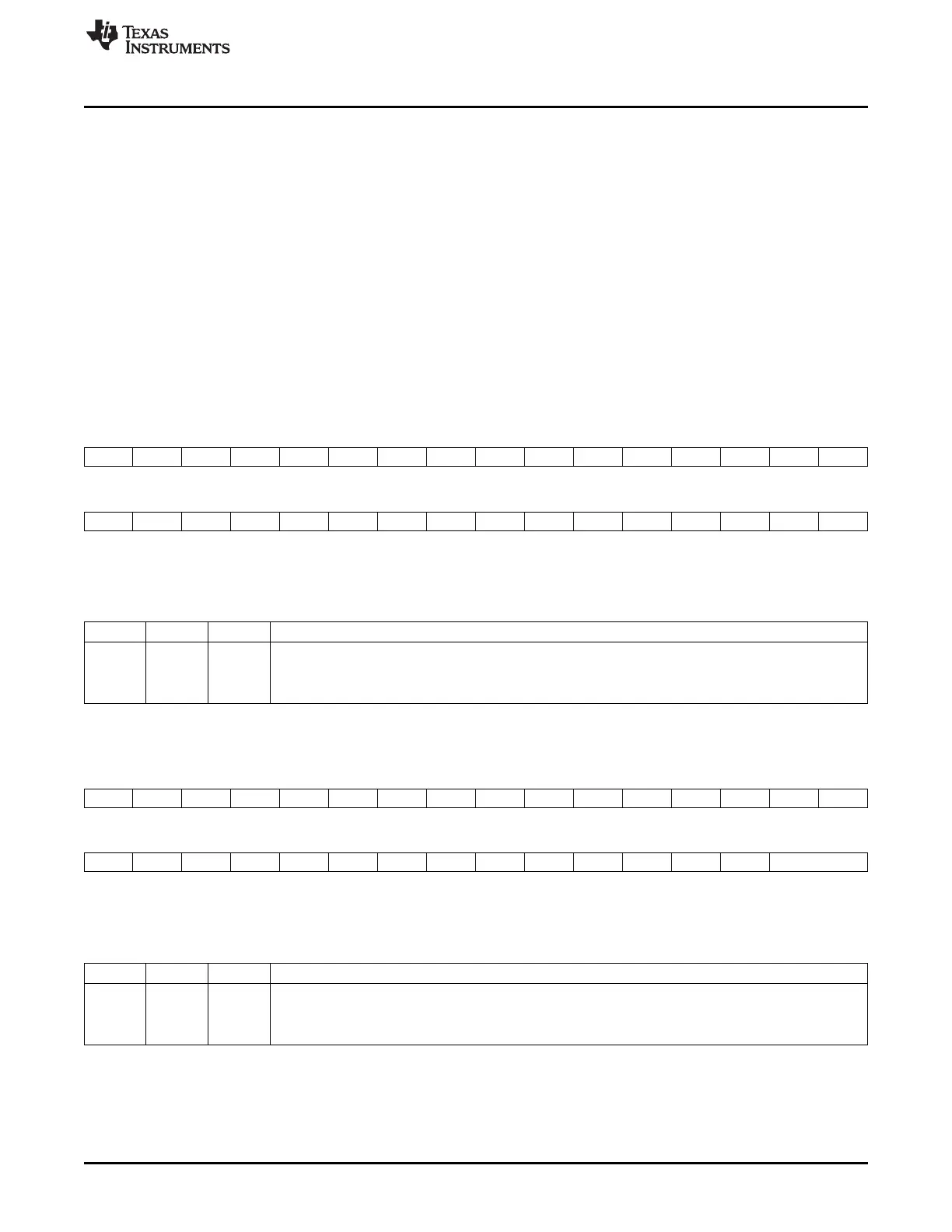

Figure 11-89. Interrupt Enable Register High (IERH)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

I63 I62 I61 I60 I59 I58 I57 I56 I55 I54 I53 I52 I51 I50 I49 I48

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

I47 I46 I45 I44 I43 I42 I41 I40 I39 I38 I37 I36 I35 I34 I33 I32

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 11-73. Interrupt Enable Register High (IERH) Field Descriptions

Bit Field Value Description

31-0 En Interrupt enable for channels 32-63.

0 Interrupt is not enabled.

1 Interrupt is enabled.

11.4.1.7.2 Interrupt Enable Clear Register (IECR, IECRH)

The interrupt enable clear registers (IECR/IECRH) are used to clear interrupts. Writes of 1 to the bits in

IECR/IECRH clear the corresponding interrupt bits in the interrupt enable registers (IER/IERH); writes of 0

have no effect.

981

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...