www.ti.com

Ethernet Subsystem Registers

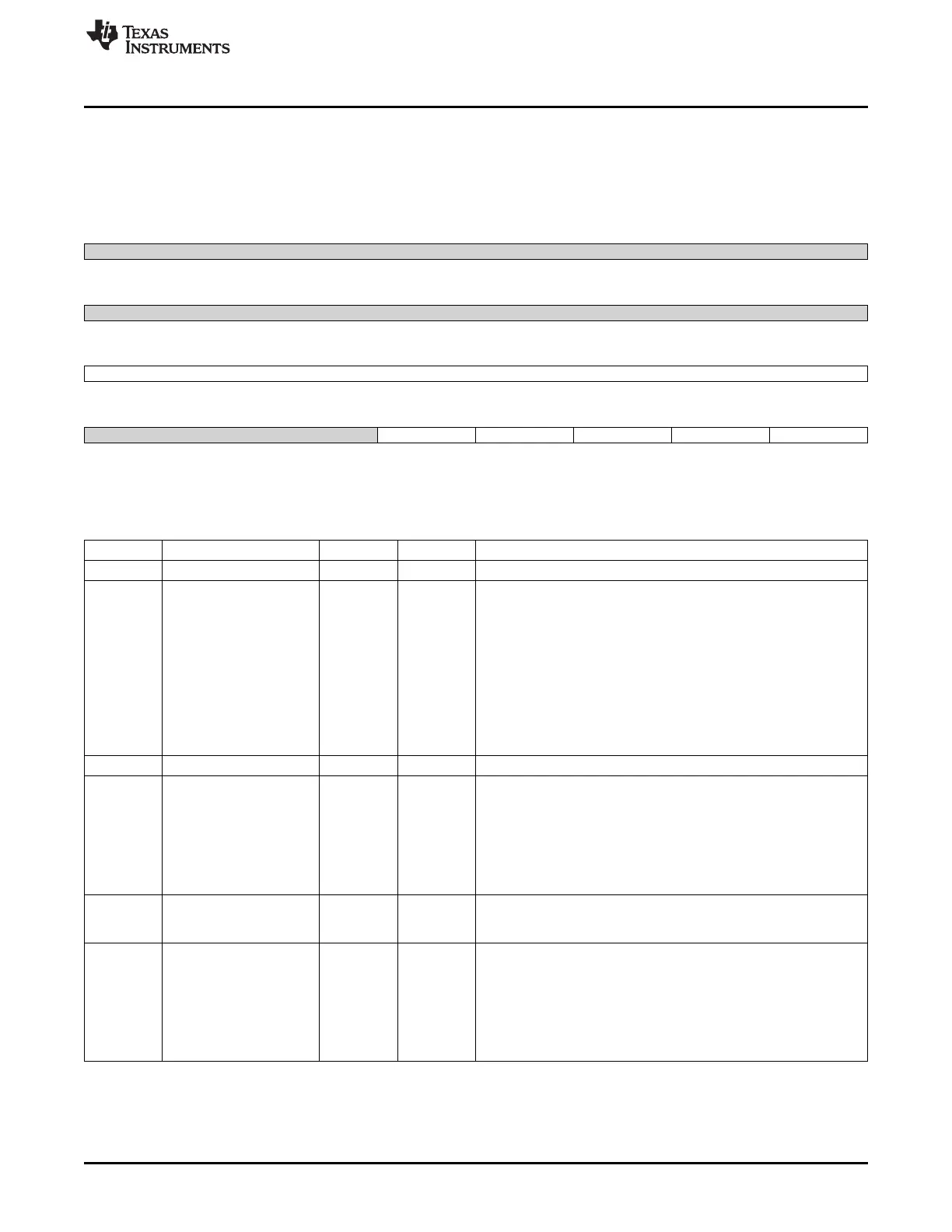

14.5.2.8 DMACONTROL Register (offset = 20h) [reset = 0h]

DMACONTROL is shown in Figure 14-36 and described in Table 14-47.

CPDMA_REGS CPDMA CONTROL REGISTER

Figure 14-36. DMACONTROL Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

TX_RLIM

R/W-0h

7 6 5 4 3 2 1 0

Reserved RX_CEF CMD_IDLE RX_OFFLEN_BLOCK RX_OWNERSHIP TX_PTYPE

R-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

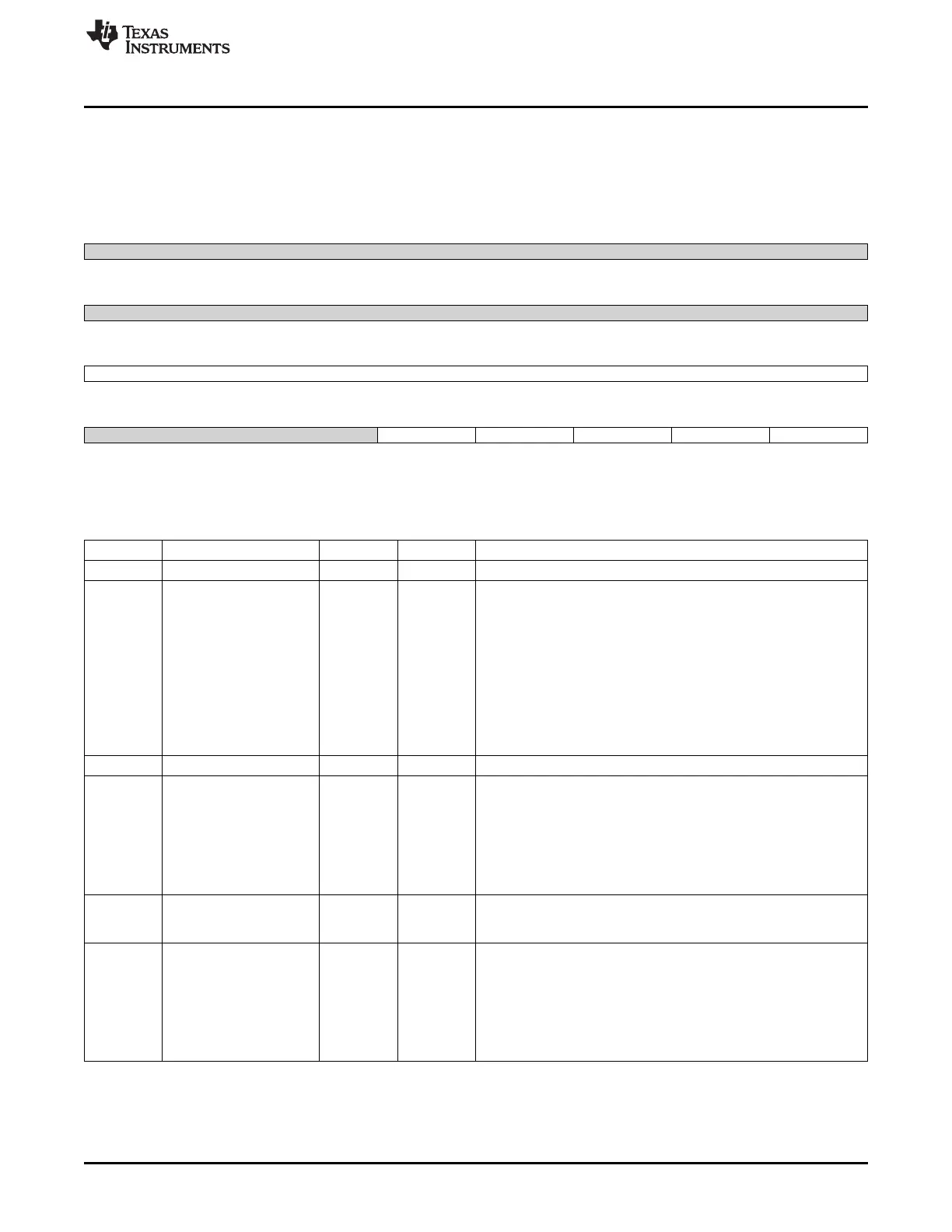

Table 14-47. DMACONTROL Register Field Descriptions

Bit Field Type Reset Description

31-16 Reserved R 0h

15-8 TX_RLIM R/W 0h Transmit Rate Limit Channel Bus

00000000 - no rate-limited channels

10000000 - channel 7 is rate-limited

11000000 - channels 7 downto 6 are rate-limited

11100000 - channels 7 downto 5 are rate-limited

11110000 - channels 7 downto 4 are rate-limited

11111000 - channels 7 downto 3 are rate-limited

11111100 - channels 7 downto 2 are rate-limited

11111110 - channels 7 downto 1 are rate-limited

11111111 - channels 7 downto 0 are rate-limited all others invalid -

this bus must be set msb towards lsb.

tx_ptype must be set if any tx_rlim bit is set for fixed priority.

7-5 Reserved R 0h

4 RX_CEF R/W 0h RX Copy Error Frames Enable - Enables DMA overrun frames to be

transferred to memory (up to the point of overrun).

The overrun error bit will be set in the frame EOP buffer descriptor.

Overrun frame data will be filtered when rx_cef is not set.

Frames coming from the receive FIFO with other error bits set are

not effected by this bit.

0 - Frames containing overrun errors are filtered.

1 - Frames containing overrun errors are transferred to memory.

3 CMD_IDLE R/W 0h Command Idle

0 - Idle not commanded

1 - Idle Commanded (read idle in DMAStatus)

2 RX_OFFLEN_BLOCK R/W 0h Receive Offset/Length word write block.

0 - Do not block the DMA writes to the receive buffer descriptor

offset/buffer length word.

The offset/buffer length word is written as specified in CPPI 3.0.

1 - Block all CPDMA DMA controller writes to the receive buffer

descriptor offset/buffer length words during CPPI packet processing.

when this bit is set, the CPDMA will never write the third word to any

receive buffer descriptor.

1265

SPRUH73H–October 2011–Revised April 2013 Ethernet Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...