DMTimer

www.ti.com

20.1.5.13 TWPS Register (offset = 48h) [reset = 0h]

TWPS is shown in Figure 20-21 and described in Table 20-23.

In posted mode the software must read the pending write status bits (Timer Write Posted Status register

bits [4:0]) to insure that following write access will not be discarded due to on going write synchronization

process. These bits are automatically cleared by internal logic when the write to the corresponding register

is acknowledged.

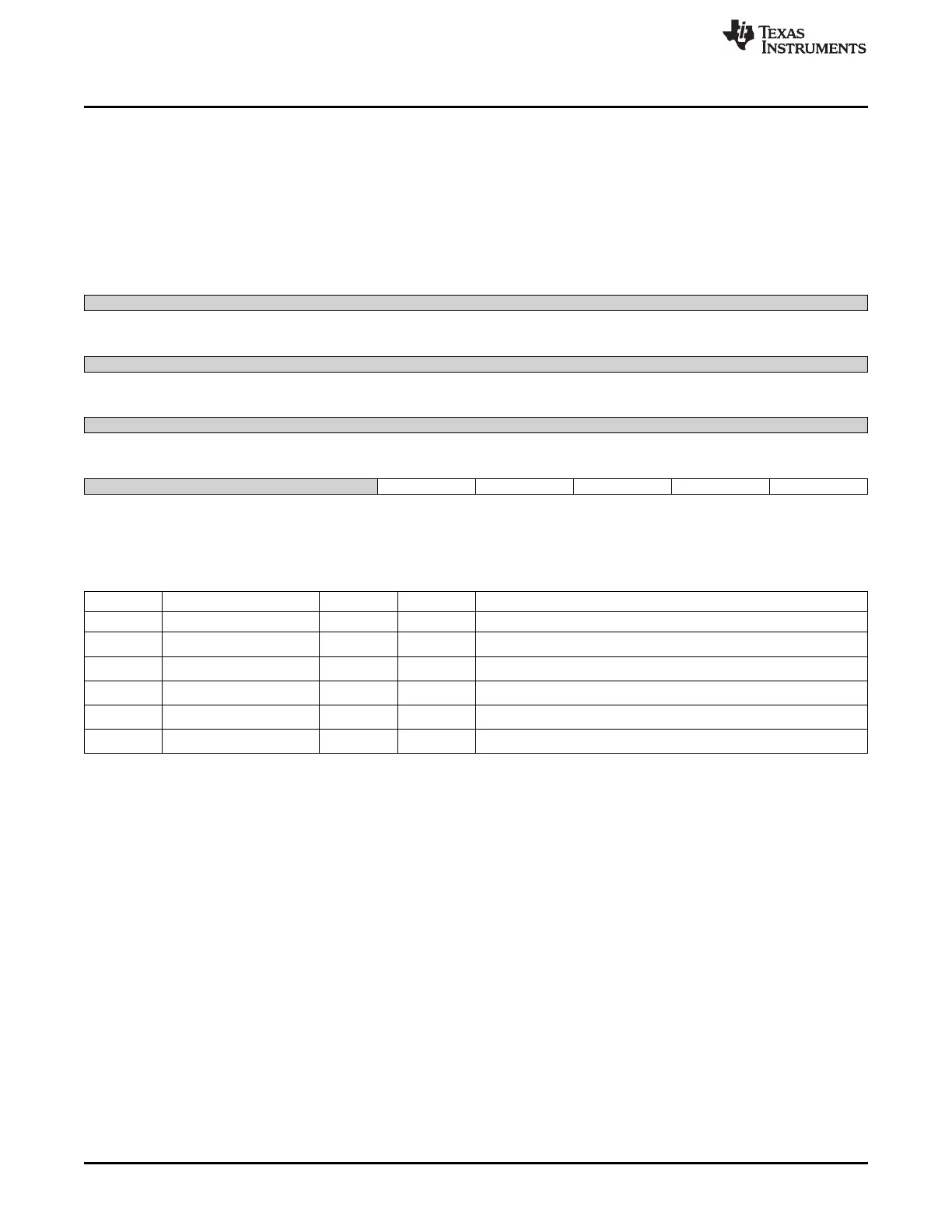

Figure 20-21. TWPS Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved

R-0h

7 6 5 4 3 2 1 0

Reserved W_PEND_TMAR W_PEND_TTGR W_PEND_TLDR W_PEND_TCRR W_PEND_TCLR

R-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

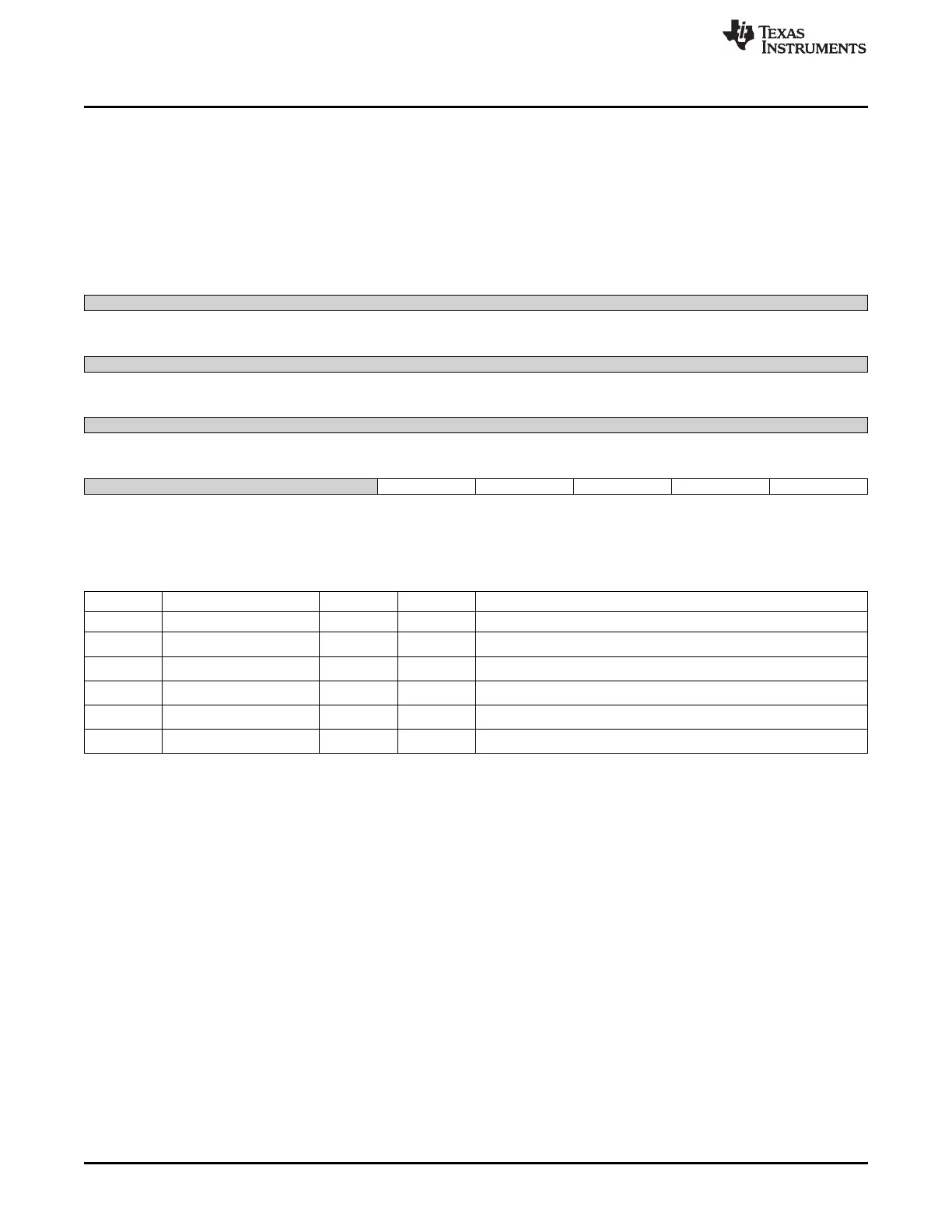

Table 20-23. TWPS Register Field Descriptions

Bit Field Type Reset Description

31-5 Reserved R 0h

4 W_PEND_TMAR R/W 0h

When equal to 1, a write is pending to the TMAR register

3 W_PEND_TTGR R/W 0h

When equal to 1, a write is pending to the TTGR register

2 W_PEND_TLDR R/W 0h

When equal to 1, a write is pending to the TLDR register

1 W_PEND_TCRR R/W 0h

When equal to 1, a write is pending to the TCRR register

0 W_PEND_TCLR R/W 0h

When equal to 1, a write is pending to the TCLR register

3580

Timers SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...