www.ti.com

EMIF

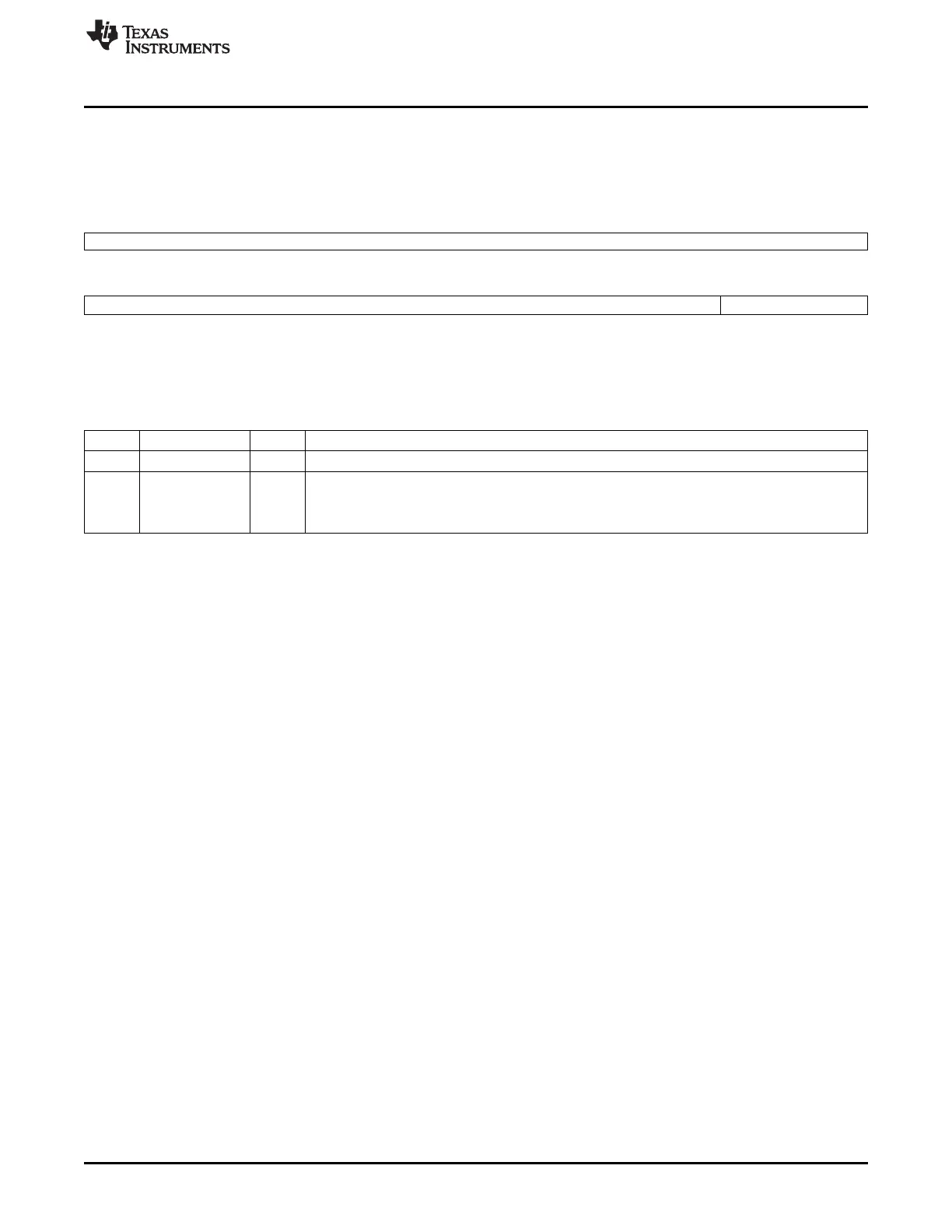

7.3.6.12 DDR PHY Data Macro 0/1 Delay Selection Register (DATA0/1_REG_PHY_USE_RANK0_DELAYS)

The DATA0/1_REG_PHY_USE_RANK0_DELAYS is shown in Figure 7-139 and described in Table 7-162.

Figure 7-139. DDR PHY Data Macro 0/1 Delay Selection Register

(DATA0/1_REG_PHY_USE_RANK0_DELAYS)

31 16

Reserved

R-0

15 1 0

Reserved RANK0 _DELAY

R-0 W-1

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

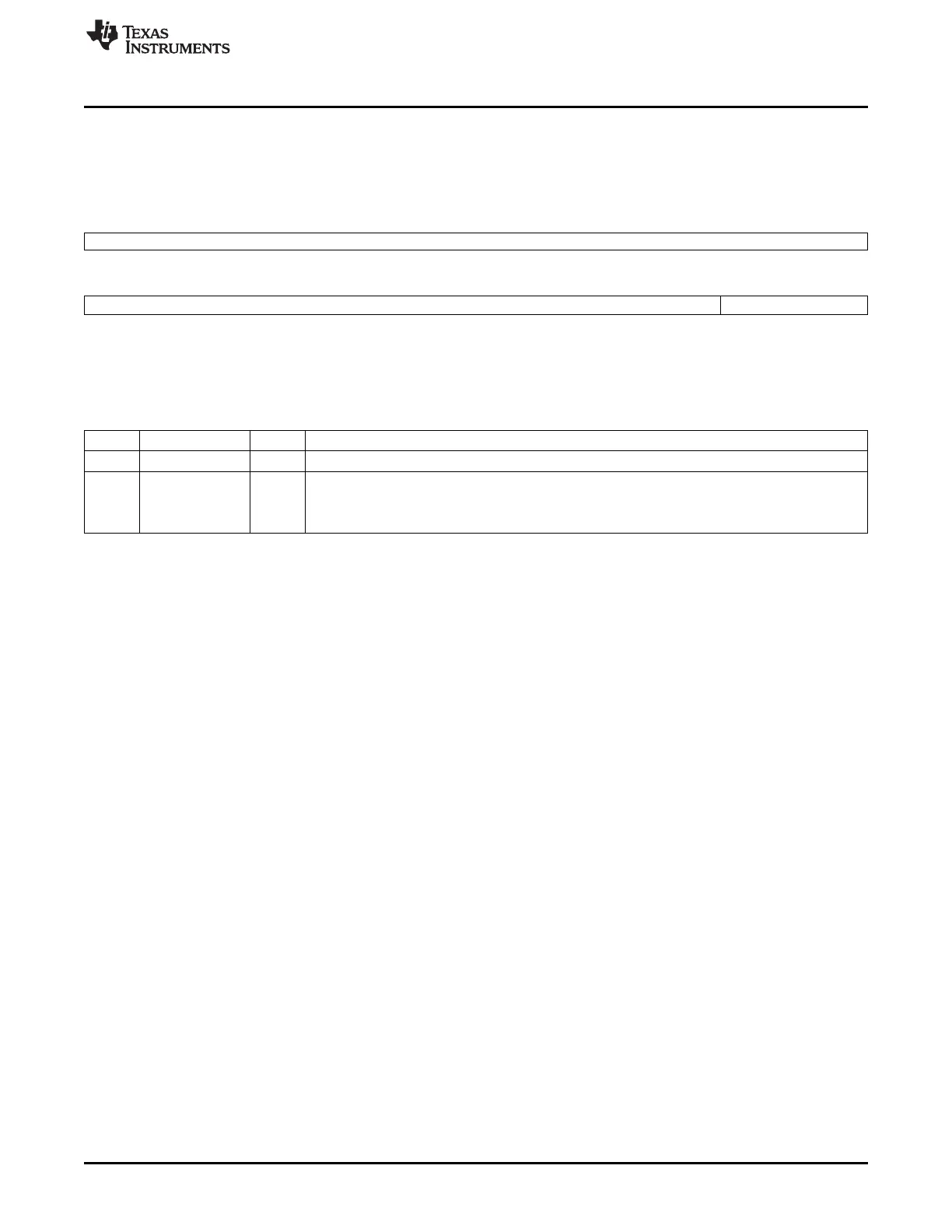

Table 7-162. DDR PHY Data Macro 0/1 Delay Selection Register

(DATA0/1_REG_PHY_USE_RANK0_DELAYS) Field Descriptions

Bit Field Value Description

31-1 Reserved 0 Reserved

0 PHY_USE_RANK Delay Selection

0_DELAYS_0

0 Each Rank uses its own delay. (Recommended). This is applicable only in case of DDR3

1 Rank 0 delays are used for all ranks. This must be set to 1 for DDR2 and mDDR.

475

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...