Power, Reset, and Clock Management

www.ti.com

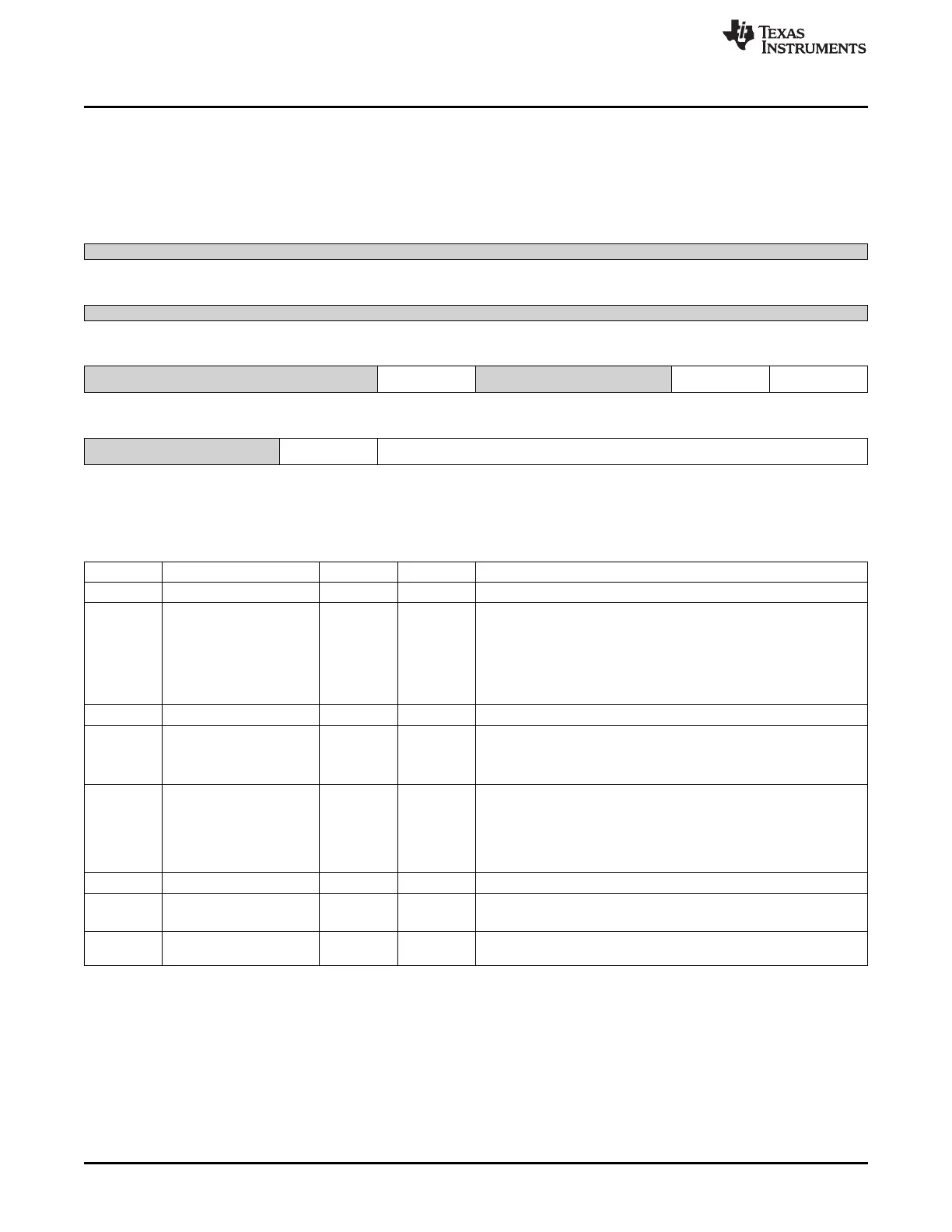

8.1.12.2.33 CM_DIV_M4_DPLL_CORE Register (offset = 80h) [reset = 4h]

CM_DIV_M4_DPLL_CORE is shown in Figure 8-116 and described in Table 8-124.

This register provides controls over the CLKOUT1 o/p of the HSDIVIDER.

Figure 8-116. CM_DIV_M4_DPLL_CORE Register

31 30 29 28 27 26 25 24

Reserved

R-0h

23 22 21 20 19 18 17 16

Reserved

R-0h

15 14 13 12 11 10 9 8

Reserved HSDIVIDER_CLKOUT Reserved ST_HSDIVIDER_CLK HSDIVIDER_CLKOUT

1_PWDN OUT1 1_GATE_CTRL

R-0h R/W-0h R-0h R-0h R/W-0h

7 6 5 4 3 2 1 0

Reserved HSDIVIDER_CLKOUT HSDIVIDER_CLKOUT1_DIV

1_DIVCHACK

R-0h R-0h R/W-4h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

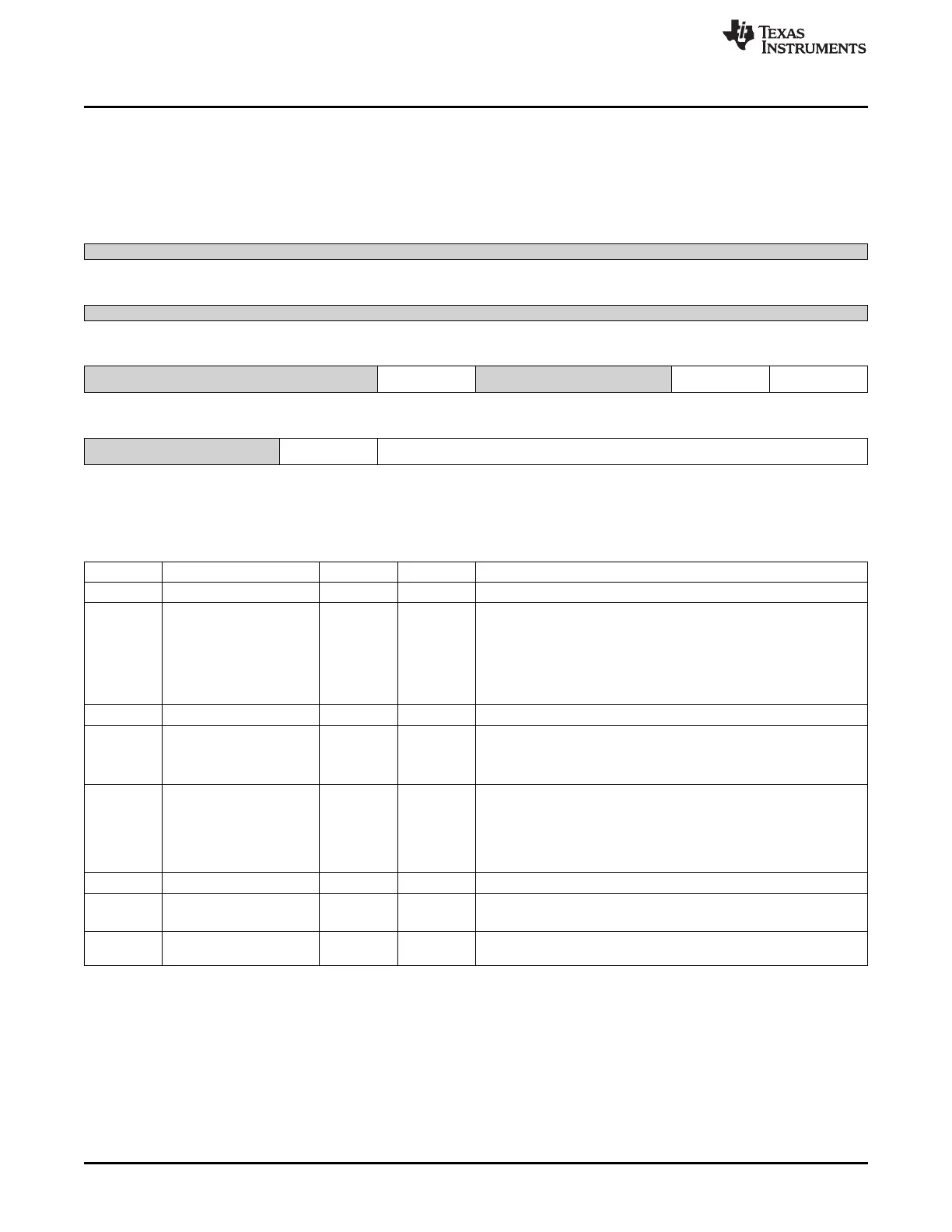

Table 8-124. CM_DIV_M4_DPLL_CORE Register Field Descriptions

Bit Field Type Reset Description

31-13 Reserved R 0h

12 HSDIVIDER_CLKOUT1_P R/W 0h

Automatic power down for HSDIVIDER M4 divider and hence

WDN

CLKOUT1 output when the o/p clock is gated.

0x0 = ALWAYS_ACTIVE : Keep M4 divider powered on even when

CLKOUT1 is gated.

0x1 = AUTO_PWDN : Automatically power down M4 divider when

CLKOUT1 is gated.

11-10 Reserved R 0h

9 ST_HSDIVIDER_CLKOU R 0h

HSDIVIDER CLKOUT1 status

T1

0x0 = CLK_ENABLED : The clock output is enabled

0x1 = CLK_GATED : The clock output is gated

8 HSDIVIDER_CLKOUT1_ R/W 0h

Control gating of HSDIVIDER CLKOUT1

GATE_CTRL

0x0 = CLK_AUTOGATE : Automatically gate this clock when there is

no dependency for it

0x1 = CLK_ENABLE : Force this clock to stay enabled even if there

is no request

7-6 Reserved R 0h

5 HSDIVIDER_CLKOUT1_ R 0h

Toggle on this status bit after changing HSDIVIDER_CLKOUT1_DIV

DIVCHACK

indicates that the change in divider value has taken effect

4-0 HSDIVIDER_CLKOUT1_ R/W 4h DPLL post-divider factor, M4, for internal clock generation.

DIV Divide values from 1 to 31.

648

Power, Reset, and Clock Management (PRCM) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...