Multimedia Card Registers

www.ti.com

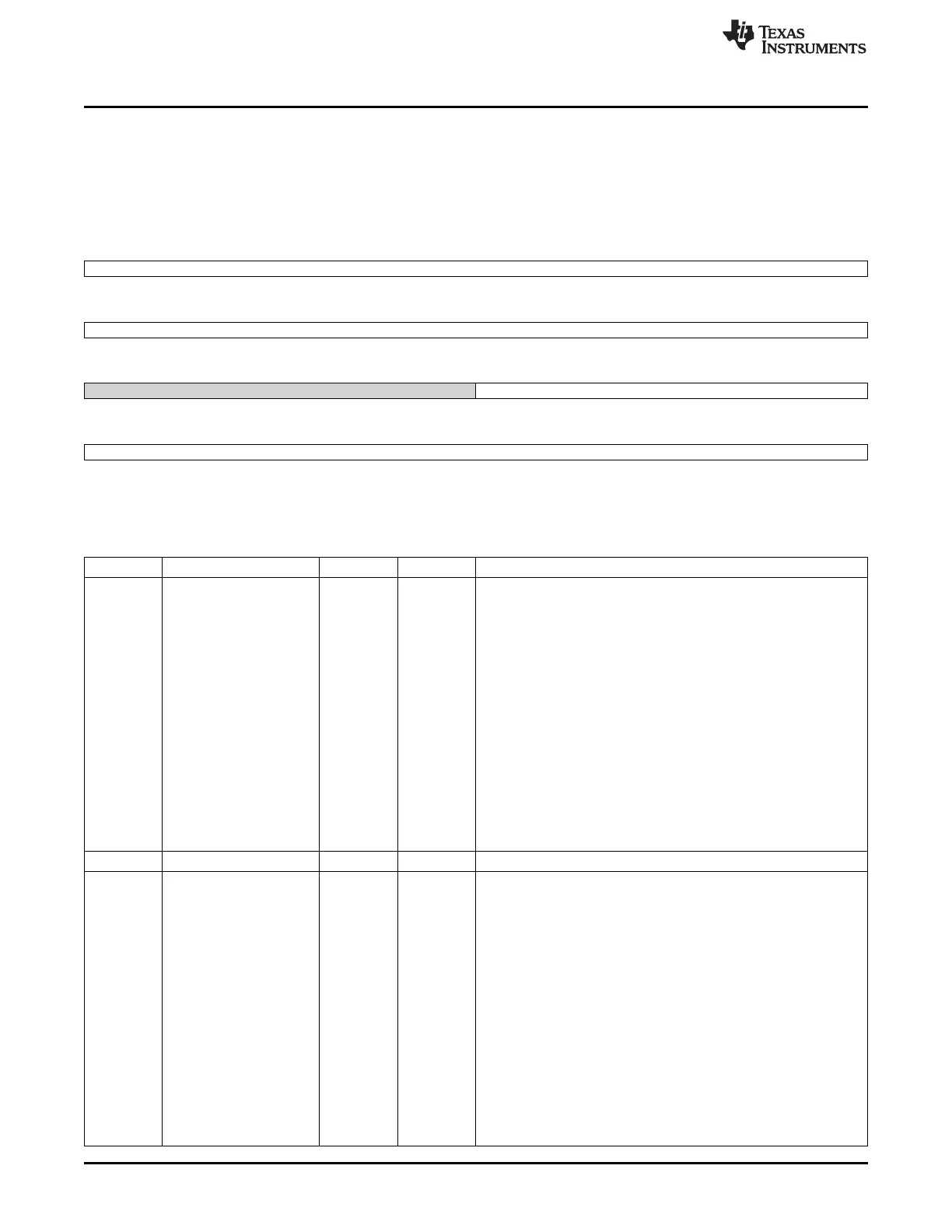

18.5.1.8 SD_BLK Register (offset = 204h) [reset = 0h]

SD_BLK is shown in Figure 18-44 and described in Table 18-27.

This register shall be used for any card. SD_BLK[BLEN] is the block size register. SD_BLK[NBLK] is the

block count register.

Figure 18-44. SD_BLK Register

31 30 29 28 27 26 25 24

NBLK

R/W-0h

23 22 21 20 19 18 17 16

NBLK

R/W-0h

15 14 13 12 11 10 9 8

Reserved BLEN

R-0h R/W-0h

7 6 5 4 3 2 1 0

BLEN

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

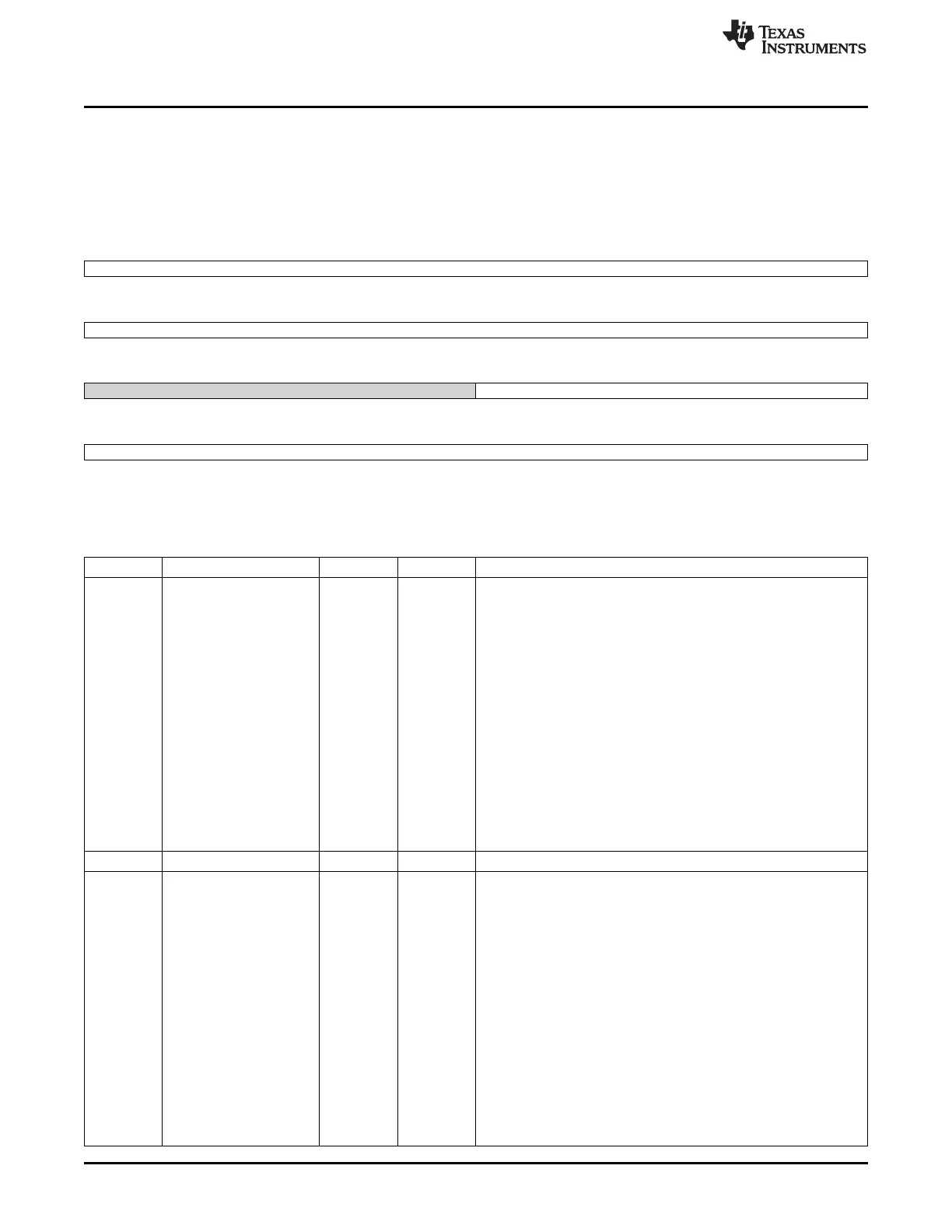

Table 18-27. SD_BLK Register Field Descriptions

Bit Field Type Reset Description

31-16 NBLK R/W 0h Blocks count for current transfer.

This register is enabled when Block count Enable (SD_CMD[1] BCE

bit) is set to 1 and is valid only for multiple block transfers.

Setting the block count to 0 results no data blocks being transferred.

Note: The host controller decrements the block count after each

block transfer and stops when the count reaches zero.

This register can be accessed only if no transaction is executing

(i.e., after a transaction has stopped).

Read operations during transfers may return an invalid value and

write operation will be ignored.

In suspend context, the number of blocks yet to be transferred can

be determined by reading this register.

When restoring transfer context prior to issuing a Resume command,

The local host shall restore the previously saved block count.

0x0 = Stop count

0x1 = 1 block

0x2 = 2 blocks

0xffff = 65535 blocks

15-12 Reserved R 0h

11-0 BLEN R/W 0h Transfer block size.

This register specifies the block size for block data transfers.

Read operations during transfers may return an invalid value, and

write operations are ignored.

When a CMD12 command is issued to stop the transfer, a read of

the BLEN field after transfer completion (SD_STAT[1] TC bit set to

1) will not return the true byte number of data length while the stop

occurs but the value written in this register before transfer is

launched.

0x0 = No data transfer

0x1 = 1 byte block length

0x2 = 2 bytes block length

0x3 = 3 bytes block length

0x1ff = 511 bytes block length

0x200 = 512 bytes block length

0x7ff = 2047 bytes block length

0x800 = 2048 bytes block length

3404

Multimedia Card (MMC) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...