CONTROL_MODULE Registers

www.ti.com

9.3.5 control_emif_sdram_config Register (offset = 110h) [reset = 0h]

The CONTROL_EMIF_SDRAM_CONFIG register exports SDRAM configuration information to the EMIF

after resuming from low power scenarios.

This register should be loaded with the same value as SDRAM_CONFIG during DDR initialization.

control_emif_sdram_config is shown in Figure 9-8 and described in Table 9-15.

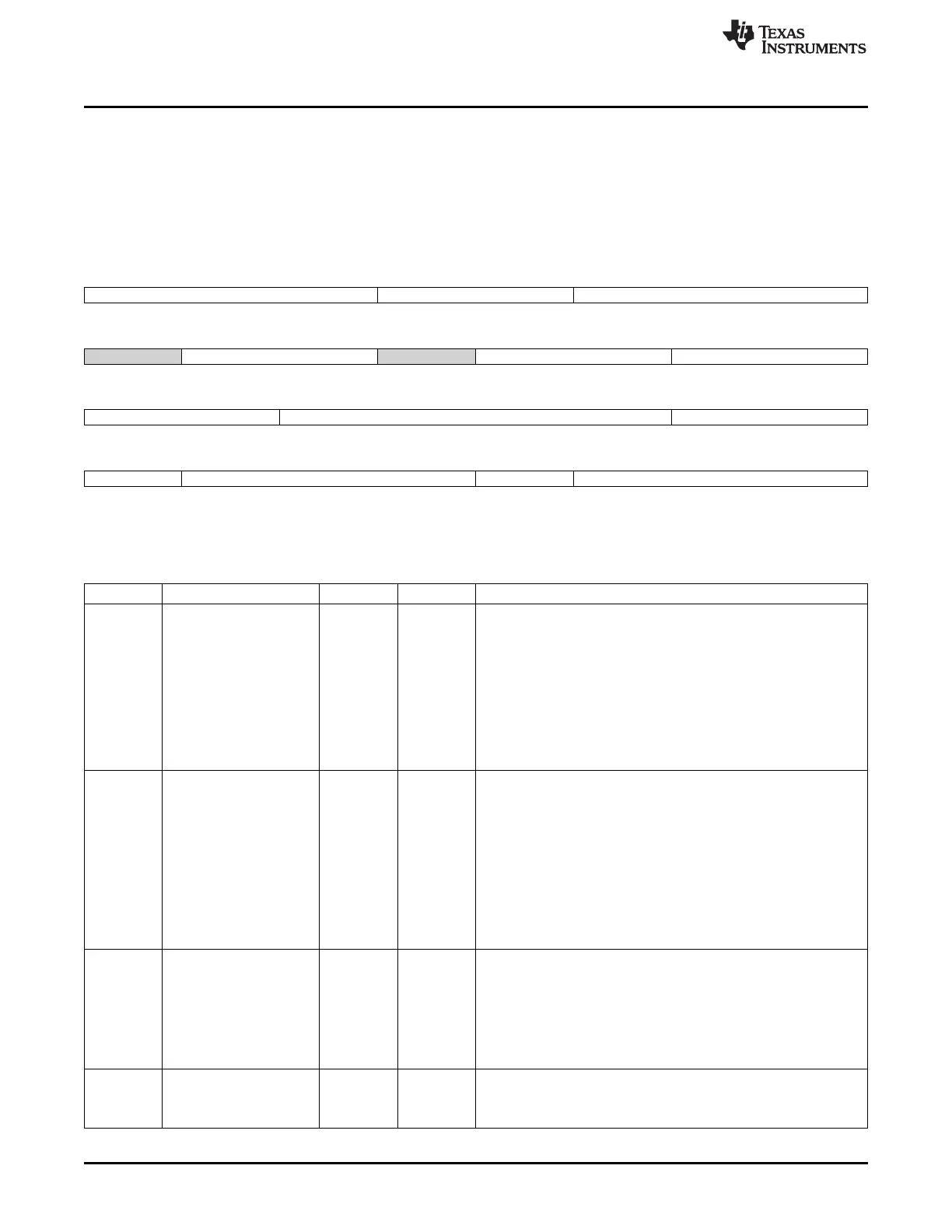

Figure 9-8. control_emif_sdram_config Register

31 30 29 28 27 26 25 24

SDRAM_TYPE IBANK_POS DDR_TERM

R/W-0h R/W-0h R/W-0h

23 22 21 20 19 18 17 16

Reserved DYN_ODT Reserved SDRAM_DRIVE CWL

R-0h R/W-0h R-0h R/W-0h R/W-0h

15 14 13 12 11 10 9 8

NARROW_MODE CL ROWSIZE

R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

ROWSIZE IBANK EBANK PAGESIZE

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

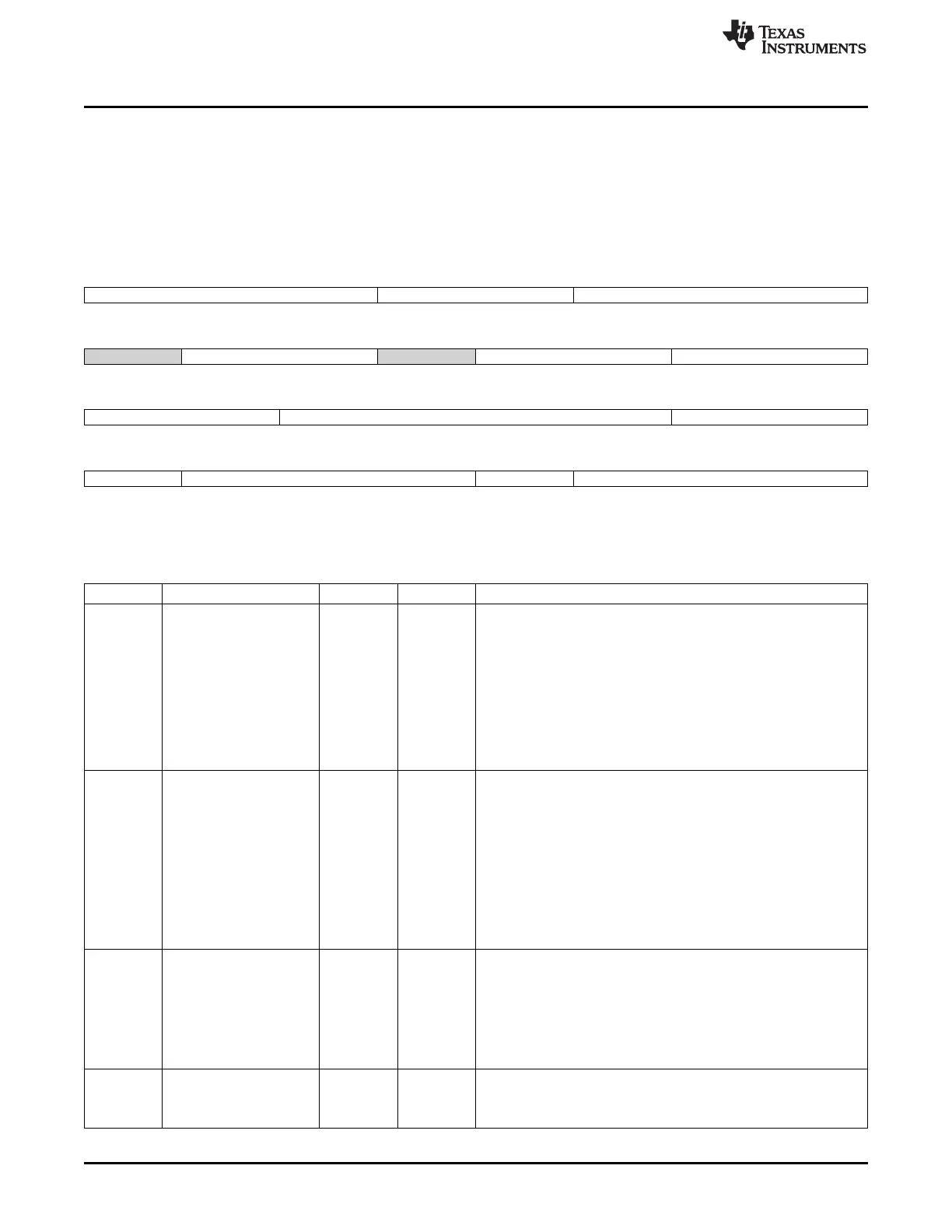

Table 9-15. control_emif_sdram_config Register Field Descriptions

Bit Field Type Reset Description

31-29 SDRAM_TYPE R/W 0h

SDRAM Type selection

000 – Reserved

001 – LPDDR1

010 – DDR2

011 – DDR3

100 – Reserved

101 – Reserved

110 – Reserved

111 – Reserved

28-27 IBANK_POS R/W 0h

Internal bank position.

00 - All Bank Address bits assigned from OCP address above

column address bits.

01 – Bank Address bits [1:0] assigned from OCP address above

column address bits and bit [2] from OCP address bits above row

address bits.

10 – Bank Address bit [0] assigned from OCP address above

column address bits and bit [2:1] from OCP address bits above row

address bits.

11 – All Bank Address bits assigned from OCP address bits above

row address bits.

26-24 DDR_TERM R/W 0h

DDR2 and DDR3 termination resistor value. Set to 0 to disable

termination.

For DDR2, set to 1 for 75 ohm, set to 2 for 150 ohm, and set to 3 for

50 ohm.

For DDR3, set to 1 for RZQ/4, set to 2 for RZQ/2, set to 3 for RZQ/6,

set to 4 for RZQ/12, and set to 5 for RZQ/8.

All other values are reserved.

23 DDR2_DDQS R/W 0h

DDR2 differential DQS enable.

Set to 0 for single ended DQS.

Set to 1 for differential DQS

766

Control Module SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...