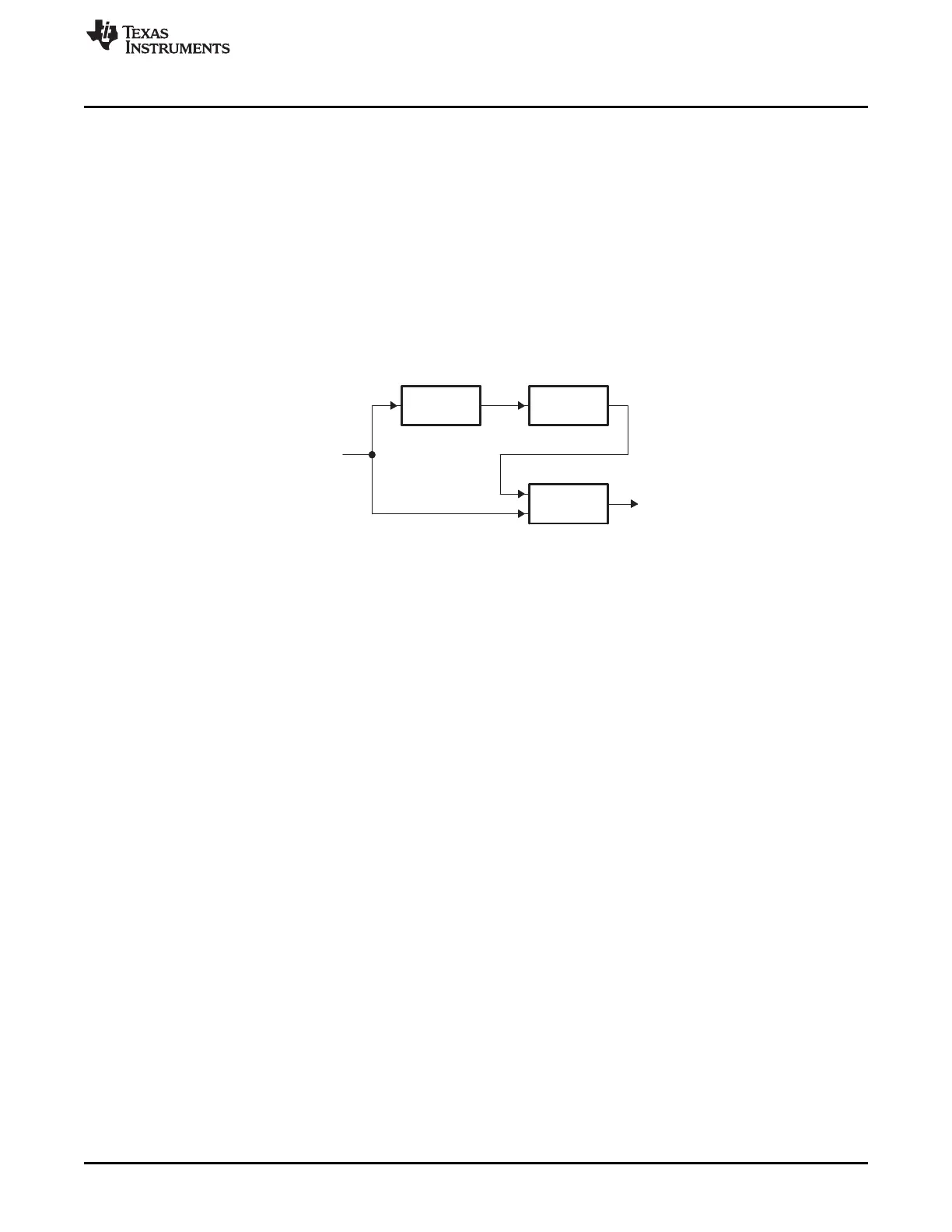

Event

combiner

selector

Interrupt

flags

Event

EVT[59:60]

(from McASP)

INT[15:4]

(to CPU)

EVT[3:0]

www.ti.com

Functional Description

22.3.13 Interrupts

22.3.13.1 Interrupt Multiplexing

The processor includes an interrupt controller (INTC) to manage CPU interrupts. The INTC maps the

device events to 12 CPU interrupts. The McASP generates 4 interrupts to the processor.

The event inputs can be routed to 12 maskable interrupts to the CPU (INT[15:4]). The INTC interrupt

selector allows the McASP system events to be routed to any of the 12 CPU interrupt inputs. Furthermore,

the INTC provides status flags and allows the combination of events, as shown in Figure 22-34. You must

properly configure the INTC by enabling, masking, and routing the McASP system events to the desired

CPU interrupts.

Figure 22-34. Interrupt Multiplexing

22.3.13.2 Transmit Data Ready Interrupt

The transmit data ready interrupt (XDATA) is generated if XDATA is 1 in the XSTAT register and XDATA

is also enabled in XINTCTL. Section 22.3.10.1.1 provides details on when XDATA is set in the XSTAT

register.

A transmit start of frame interrupt (XSTAFRM) is triggered by the recognition of transmit frame sync. A

transmit last slot interrupt (XLAST) is a qualified version of the data ready interrupt (XDATA). It has the

same behavior as the data ready interrupt, but is further qualified by having the data requested belonging

to the last slot (the slot that just ended was next-to-last TDM slot, current slot is last slot).

22.3.13.3 Receive Data Ready Interrupt

The receive data ready interrupt (RDATA) is generated if RDATA is 1 in the RSTAT register and RDATA

is also enabled in RINTCTL. Section 22.3.10.1.2 provides details on when RDATA is set in the RSTAT

register.

A receiver start of frame interrupt (RSTAFRM) is triggered by the recognition of a receiver frame sync. A

receiver last slot interrupt (RLAST) is a qualified version of the data ready interrupt (RDATA). It has the

same behavior as the data ready interrupt, but is further qualified by having the data in the buffer come

from the last TDM time slot (the slot that just ended was last TDM slot).

22.3.13.4 Error Interrupts

Upon detection, the following error conditions generate interrupt flags:

• In the receive status register (RSTAT):

– Receiver overrun (ROVRN).

– Unexpected receive frame sync (RSYNCERR).

– Receive clock failure (RCKFAIL).

– Receive DMA error (RDMAERR).

3821

SPRUH73H–October 2011–Revised April 2013 Multichannel Audio Serial Port (McASP)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...