Power, Reset, and Clock Management

www.ti.com

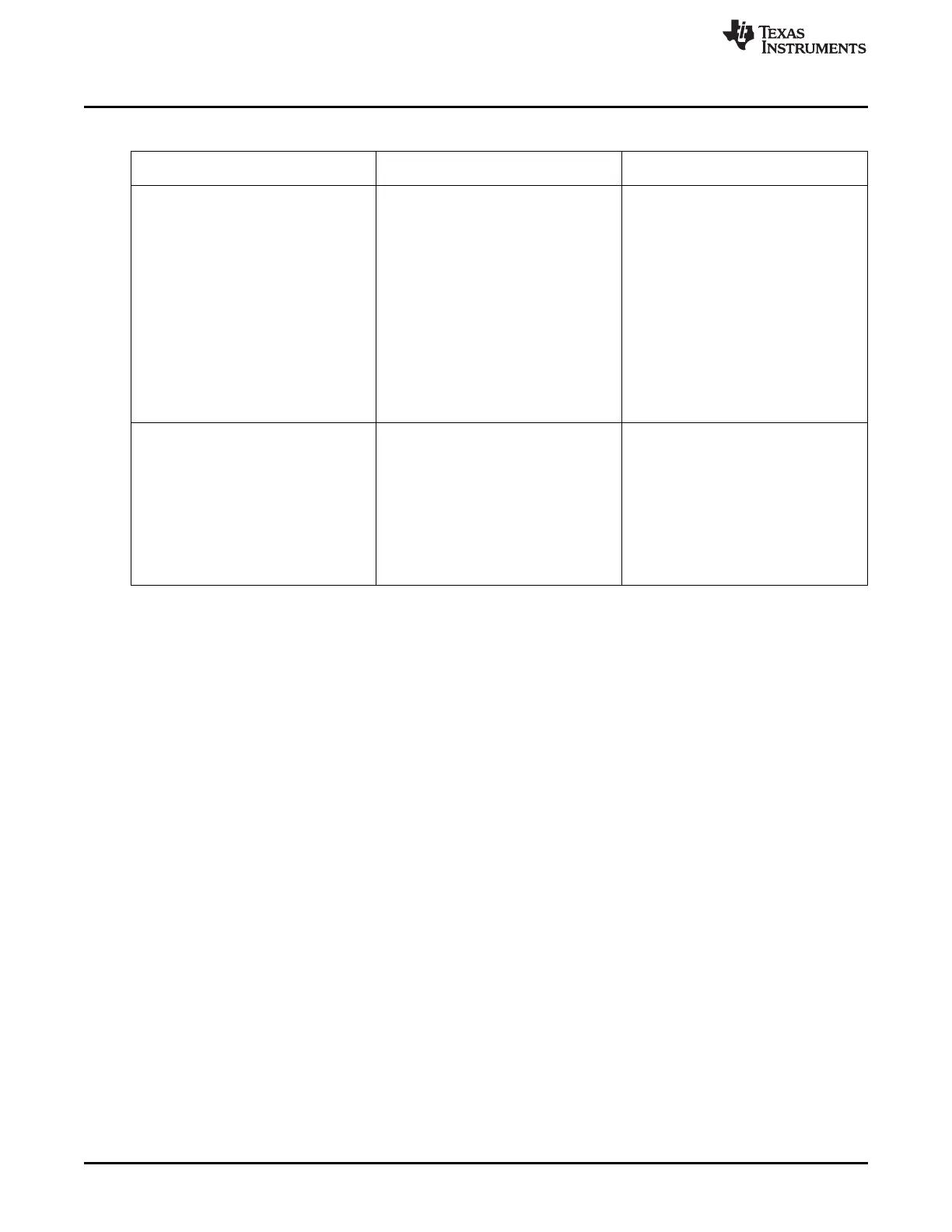

Table 8-13. Typical Power Modes (continued)

Power Modes Application State Power Domains, Clocks, and Voltage

Supply States

Deepsleep0 PD_PER peripheral and Cortex-A8/MPU

Power supplies:

register information will be lost. On-chip

All power supplies are ON.

peripheral register (context) information of

VDD_MPU = 0.95 V (nom)

PD-PER domain needs to be saved by

application to SDRAM before entering this

VDD_CORE = 0.95 V (nom)

mode. DDR is in self-refresh. For wakeup,

Clocks:

boot ROM executes and branches to

Main Oscillator (OSC0) = OFF

peripheral context restore followed by

All DPLLs are in bypass.

system resume.

Power domains:

PD_PER = OFF

PD_MPU = OFF

PD_GFX = OFF

PD_WKUP = ON

DDR is in self-refresh.

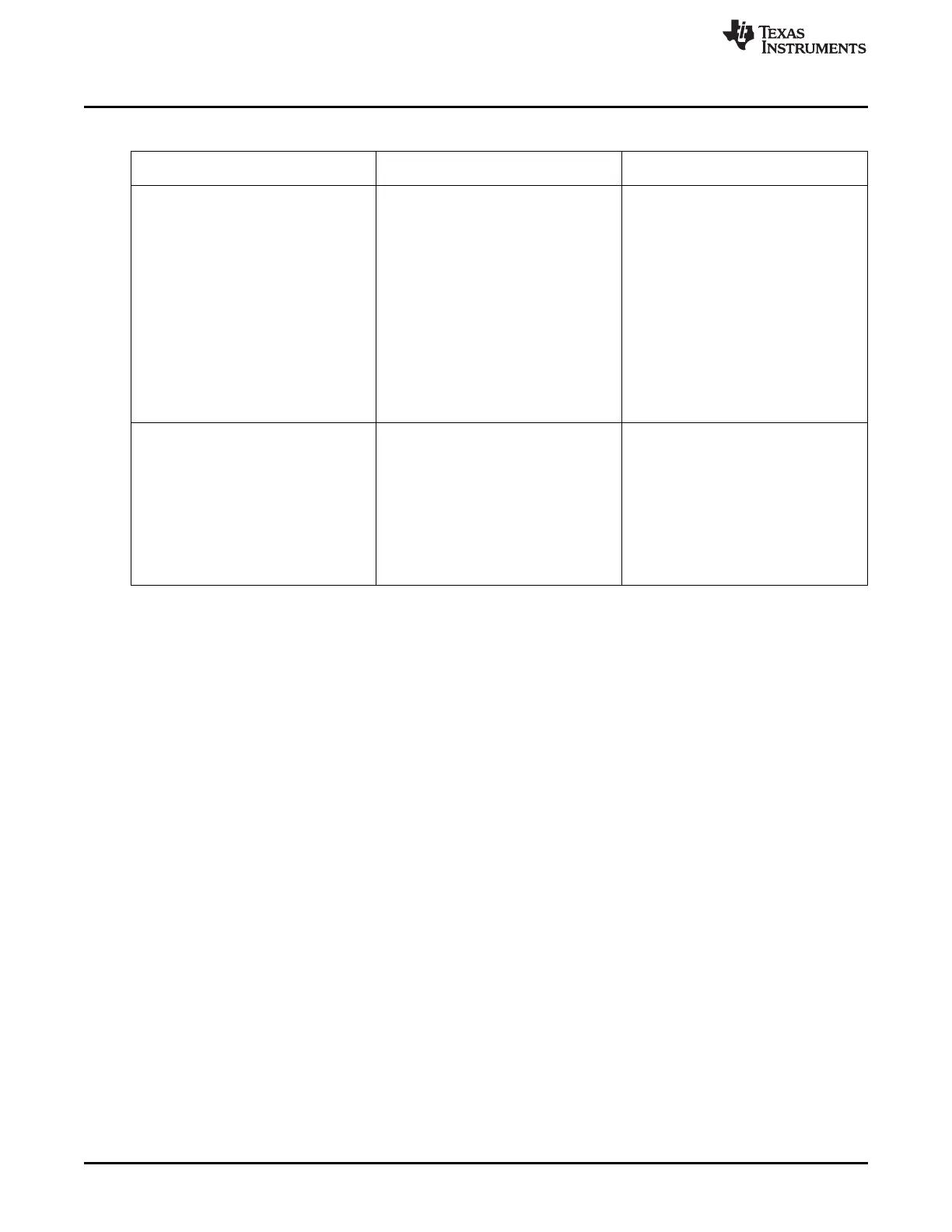

RTC-Only RTC timer remains active and all other

Power supplies:

device functionality is disabled.

All power supplies are OFF except

VDDS_RTC.

VDD_MPU = 0 V

VDD_CORE = 0 V

Clocks:

Main Oscillator (OSC0) = OFF

Power domains:

All power domains are OFF.

8.1.4.3.1 Active

In Active mode, the supply to all voltage rails must be maintained. All power domains come up in ON state

and the device is fully functional.

8.1.4.3.2 Standby

The device can be placed in Standby mode to reduce power consumption during low activity levels. This

first level of power management allows you to maintain the device context for fast resume times. The main

characteristics of this mode which distinguish it from Active mode are:

• All modules are clock gated except GPIOs

• PLLs may be placed in bypass mode if downstream clocking does not require full performance

• Voltage domains VDD_MPU and VDD_CORE voltage levels can be reduced to OPP50 levels because

the required performance of the entire device is reduced

• MPU power domain (PD_MPU) is in OFF state

• DDR memory is in low power self-refresh mode.

Further power reduction can be achieved in this mode if the RTC function is not required. See

Section 8.1.4.3.6, Internal RTC LDO.

The above conditions result in lower power consumption than Active mode but require the user to save the

MPU context to OCMC RAM or DDR to resume properly upon wakeup. Contents of the internal SRAM are

lost because PD_MPU is turned OFF. Wakeup in Standby mode is achieved using any GPIO. GPIO

wakeup is possible by switching the pad to GPIO mode and configuring the corresponding GPIO bank for

generating an interrupt to the MPUSS. Note that pads that do not have a GPIO muxmode (for example,

ADC or USB), cannot cause these wakeups. If additional or other wakeup sources are required, the

associated peripheral module clock and interconnect clock domain should remain enabled (this may

require the associated PLL to remain locked) and the module must be configured appropriately for wakeup

by configuring it to generate an interrupt to the MPUSS.

510

Power, Reset, and Clock Management (PRCM) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...