GPMC

www.ti.com

7.1.5.28 GPMC_ECCj_RESULT

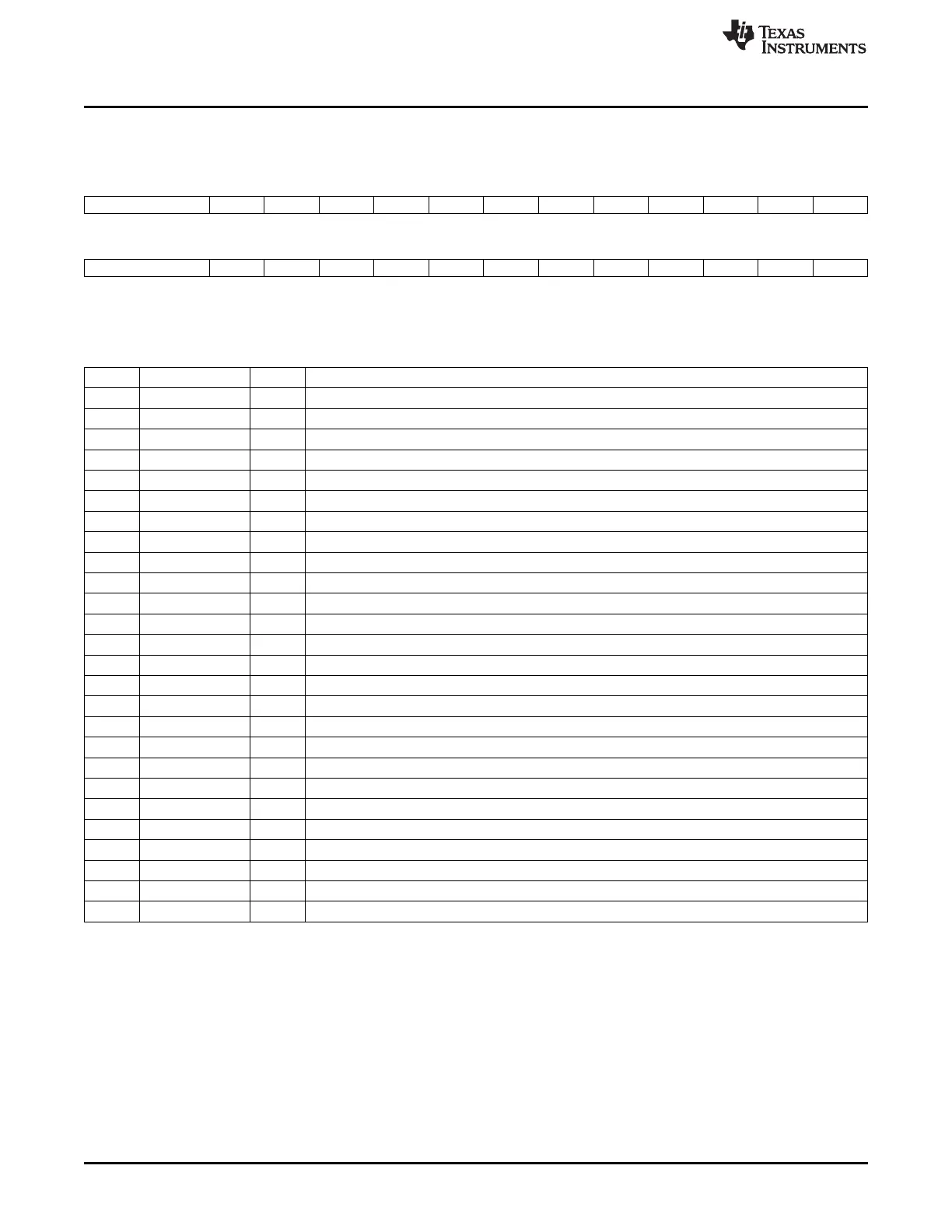

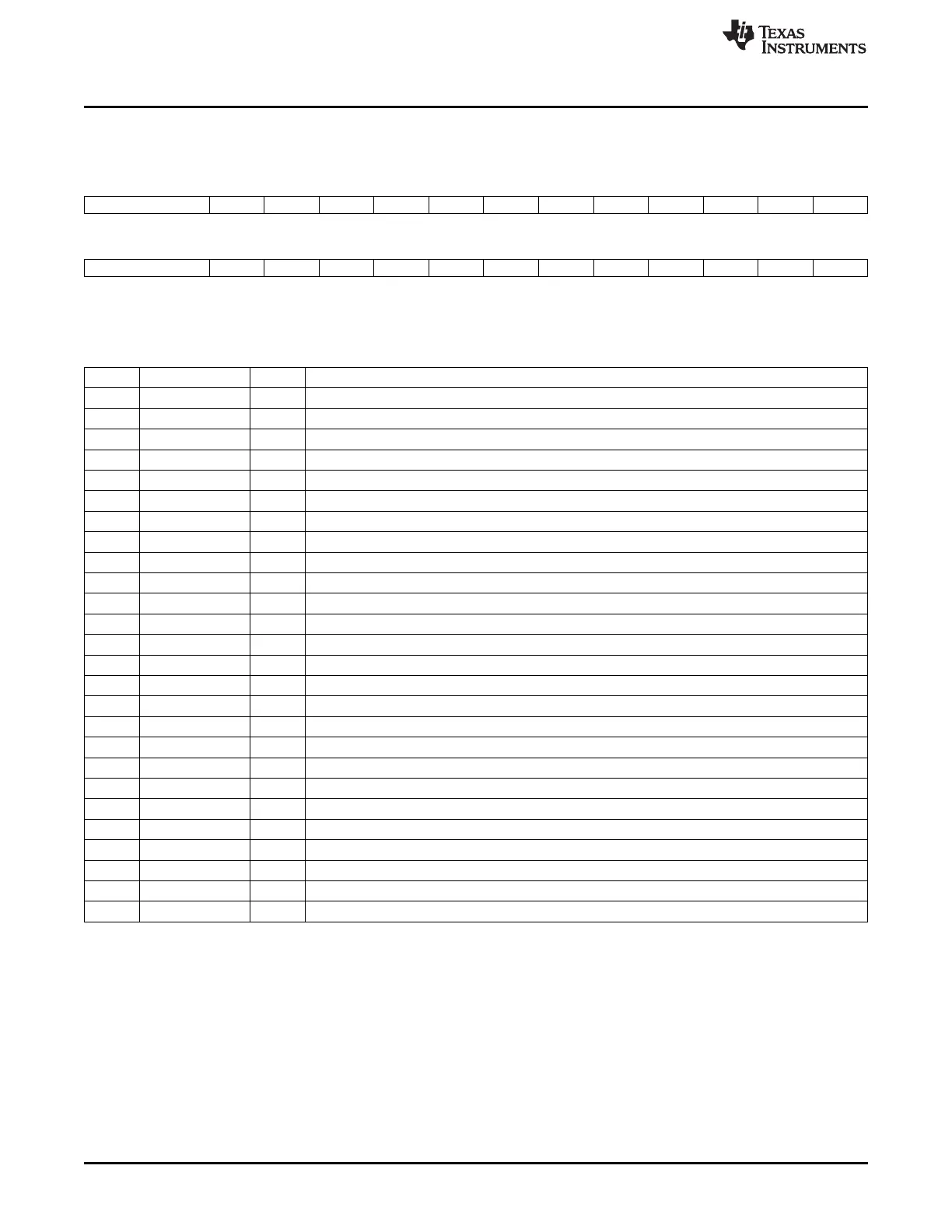

Figure 7-78. GPMC_ECCj_RESULT

31 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved P2048O P1024O P512O P256O P128O P64O P32O P16O P8O P4O P2O P1O

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

15 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved P2048E P1024E P512E P256E P128E P64E P32E P16E P8E P4E P2E P1E

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-82. GPMC_ECCj_RESULT Field Descriptions

Bit Field Value Description

31-28 Reserved 0 Reserved

27 P2048O 0-1 Odd Row Parity bit 2048, only used for ECC computed on 512 Bytes

26 P1024O 0-1 Odd Row Parity bit 1024

25 P512O 0-1 Odd Row Parity bit 512

24 P256O 0-1 Odd Row Parity bit 256

23 P128O 0-1 Odd Row Parity bit 128

22 P64O 0-1 Odd Row Parity bit 64

21 P32O 0-1 Odd Row Parity bit 32

20 P16O 0-1 Odd Row Parity bit 16

19 P8O 0-1 Odd Row Parity bit 8

18 P4O 0-1 Odd Column Parity bit 4

17 P2O 0-1 Odd Column Parity bit 2

16 P1O 0-1 Odd Column Parity bit 1

15-12 Reserved 0 Reserved

11 P2048E 0-1 Even Row Parity bit 2048, only used for ECC computed on 512 Bytes

10 P1024E 0-1 Even Row Parity bit 1024

9 P512E 0-1 Even Row Parity bit 512

8 P256E 0-1 Even Row Parity bit 256

7 P128E 0-1 Even Row Parity bit 128

6 P64E 0-1 Even Row Parity bit 64

5 P32E 0-1 Even Row Parity bit 32

4 P16E 0-1 Even Row Parity bit 16

3 P8E 0-1 Even Row Parity bit 8

2 P4E 0-1 Even Column Parity bit 4

1 P2E 0-1 Even Column Parity bit 2

0 P1E 0-1 Even Column Parity bit 1

394

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...