1, 2, 4, 8 BPP12, 16 BPP

Palette

Input

FIFO

STN

(passive)

TFT

(active)

1, 2, 4, 8 BPP 16, 24 BPP

Gray-scaler/

serializer

Output FIFO

Palette

Output FIFO

Output pins

Data source

(frame buffers)

Gray-scaler/

serializer

www.ti.com

Functional Description

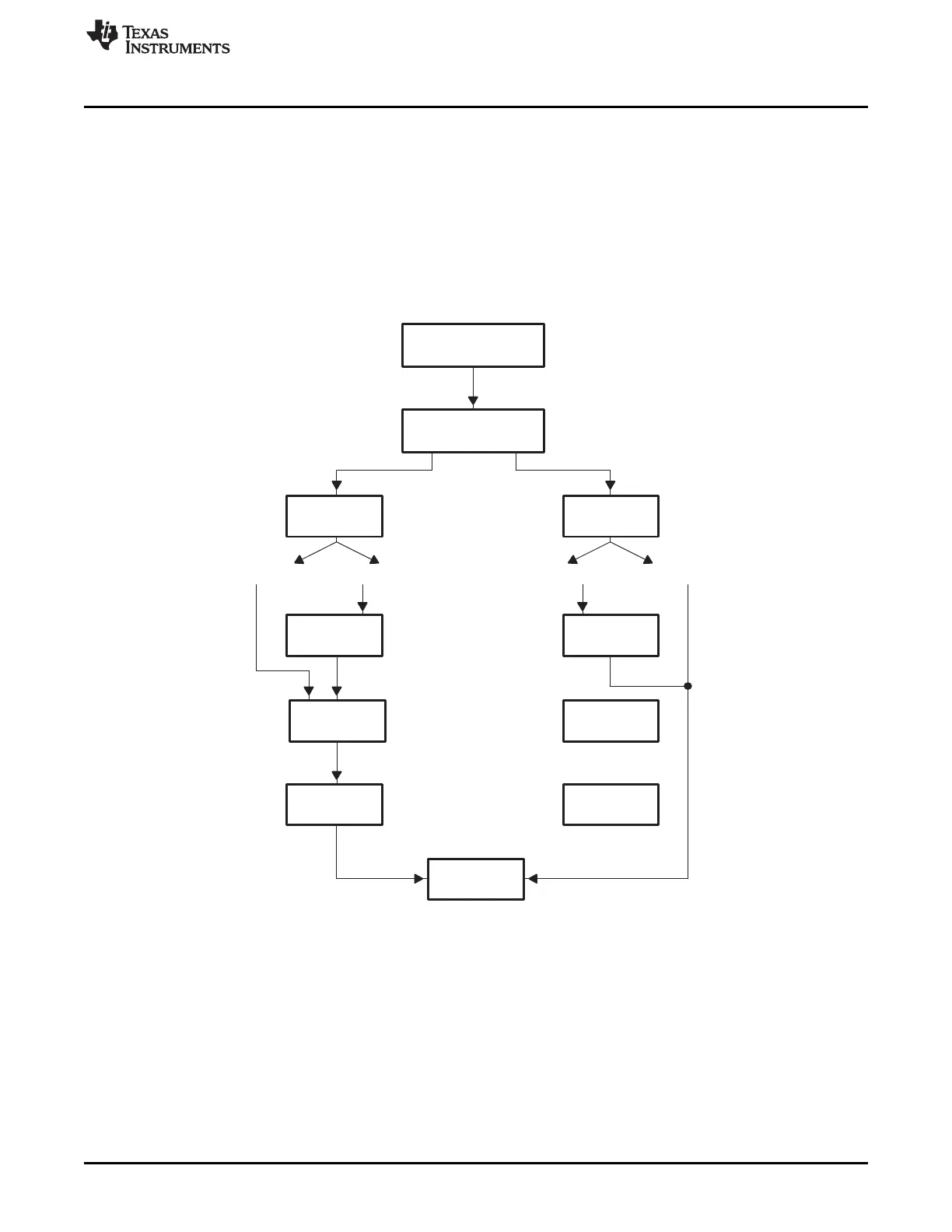

13.3.5.1 Logical Data Path

The block diagram of the Raster Controller is shown in Figure 13-1. Figure 13-4 illustrates its logical data

path for various operation modes (passive (STN) versus active (TFT), various BPP size).

Figure 13-4 shows that:

• The gray-scaler/serializer and output FIFO blocks are bypassed in active (TFT) modes.

• The palette is bypassed in both 12- and 16-BPP modes.

Figure 13-4. Logical Data Path for Raster Controller

In summary:

• The display image is stored in frame buffers.

• The built-in DMA engine constantly transfers the data stored in the frame buffers to the Input FIFO.

• The Raster Controller relays data to the external pins according to the specified format.

The remainder of this section describes the functioning blocks in Figure 13-4, including frame buffers,

palette, and gray-scaler/serializer. Their operation and programming techniques are covered in detail. The

output format is also described in Section 13.3.5.5.

1109

SPRUH73H–October 2011–Revised April 2013 LCD Controller

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...