www.ti.com

Functional Description

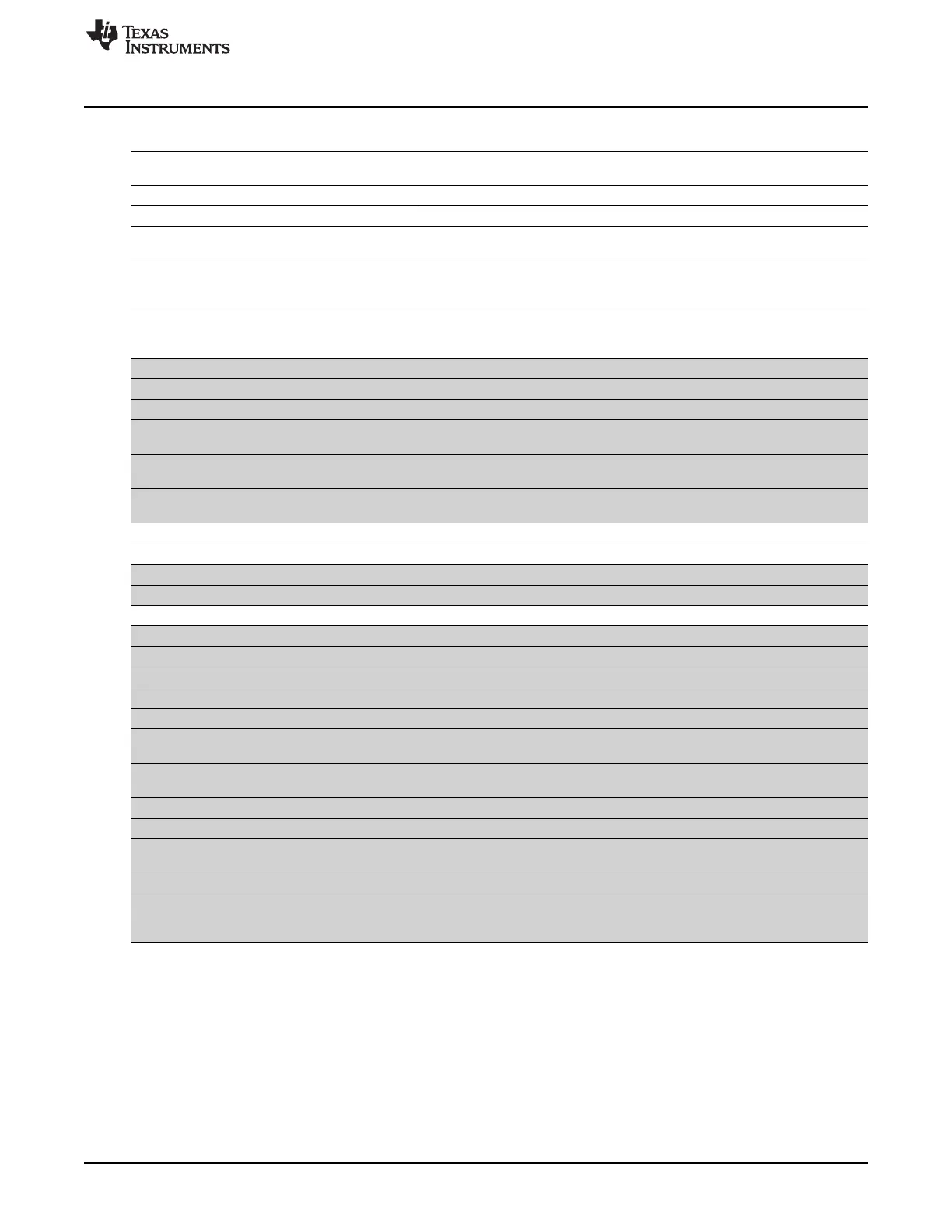

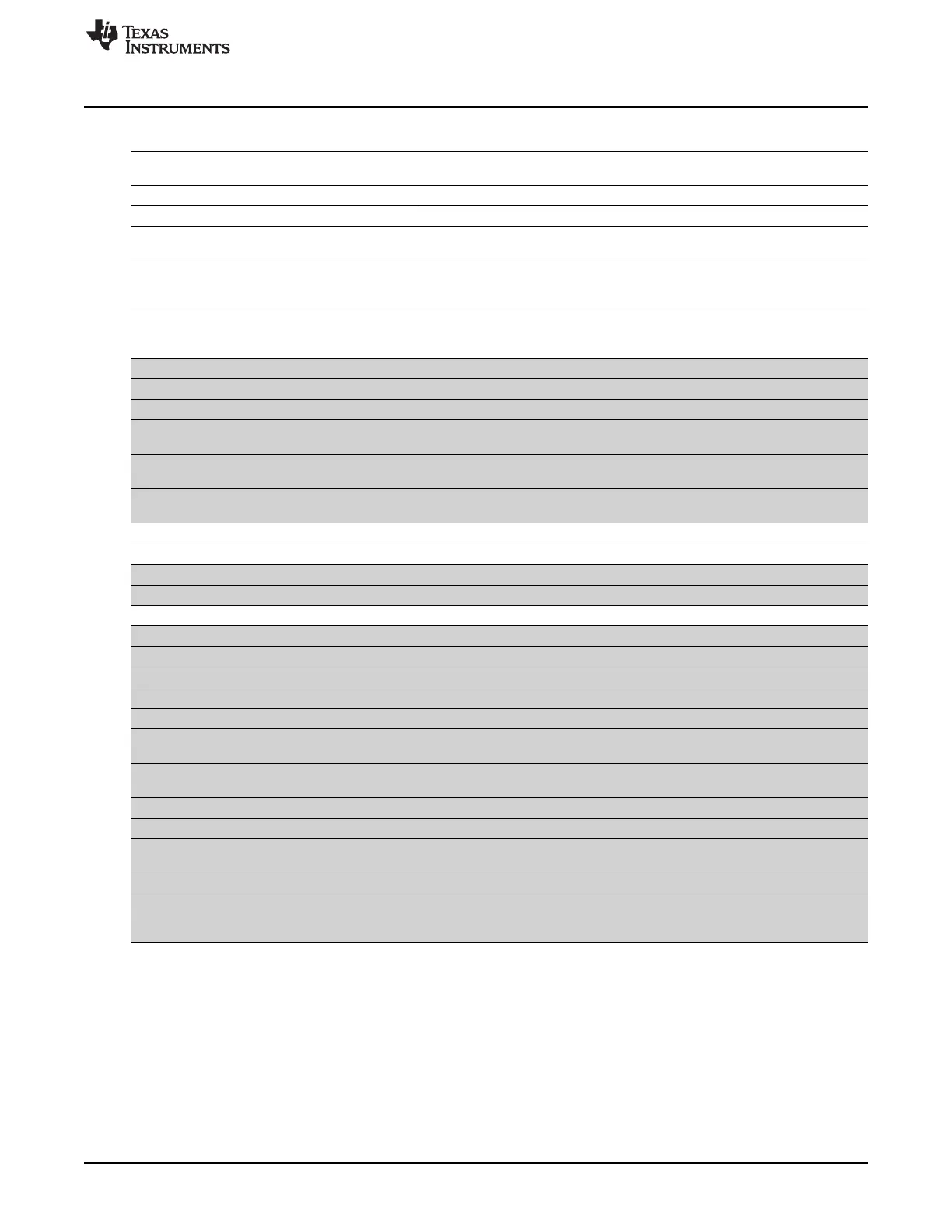

Table 19-20. UART/IrDA/CIR Register Access Mode Overview (continued)

Address Registers

Offset

Configuration Mode A Configuration Mode B Operational Mode

Read Write Read Write Read Write

0x014 UART_LSR – UART_XON2_ADD UART_XON2_AD UART_LSR –

R2 DR2

0x018 UART_MSR UART_TCR

(2)

UART_TCR UART_TCR UART_MSR UART_TCR

(2)

(1)

/UART_TCR

(2)

/UART_XOFF1

(3) (2)

/UART_XOFF1

(1)

/UART_TCR

(2)

(2) (3)

0x01C UART_SPR UART_SPR UART_TLR UART_TLR UART_SPR UART_SPR

(1)

/UART_TLR

(1)

/UART_TLR

(2) (2)

/UART_XOFF2

(3) (2)

/UART_XOFF2

(1)

/UART_TLR

(2) (1)

/UART_TLR

(2) (3) (2)

0x020 UART_MDR1 UART_MDR1 UART_MDR1 UART_MDR1 UART_MDR1 UART_MDR1

0x024 UART_MDR2 UART_MDR2 UART_MDR2 UART_MDR2 UART_MDR2 UART_MDR2

0x028 UART_SFLSR UART_TXFLL UART_SFLSR UART_TXFLL UART_SFLSR UART_TXFLL

0x02C UART_RESUM UART_TXFLH UART_RESUME UART_TXFLH UART_RESUME UART_TXFLH

E

0x030 UART_SFREG UART_RXFLL UART_SFREGL UART_RXFLL UART_SFREGL UART_RXFLL

L

0x034 UART_SFREG UART_RXFLH UART_SFREGH UART_RXFLH UART_SFREGH UART_RXFLH

H

0x038 UART_UASR – UART_UASR – UART_BLR UART_BLR

0x03C – – – – UART_ACREG UART_ACREG

0x040 UART_SCR UART_SCR UART_SCR UART_SCR UART_SCR UART_SCR

0x044 UART_SSR – UART_SSR – UART_SSR –

0x048 – – – – UART_EBLR UART_EBLR

0x050 UART_MVR – UART_MVR – UART_MVR –

0x054 UART_SYSC UART_SYSC UART_SYSC UART_SYSC UART_SYSC UART_SYSC

0x058 UART_SYSS – UART_SYSS – UART_SYSS –

0x05C UART_WER UART_WER UART_WER UART_WER UART_WER UART_WER

0x060 UART_CFPS UART_CFPS UART_CFPS UART_CFPS UART_CFPS UART_CFPS

0x064 UART_RXFIFO UART_RXFIFO_ UART_RXFIFO_LVL UART_RXFIFO_L UART_RXFIFO_LV UART_RXFIFO

_LVL LVL VL L _LVL

0x068 UART_TXFIFO UART_TXFIFO_ UART_TXFIFO_LVL UART_TXFIFO_L UART_TXFIFO_LV UART_TXFIFO

_LVL LVL VL L _LVL

0x06C UART_IER2 UART_IER2 UART_IER2 UART_IER2 UART_IER2 UART_IER2

0x070 UART_ISR2 UART_ISR2 UART_ISR2 UART_ISR2 UART_ISR2 UART_ISR2

0x074 UART_FREQ_ UART_FREQ_S UART_FREQ_SEL UART_FREQ_SE UART_FREQ_SEL UART_FREQ_

SEL EL L SEL

0x080 UART_MDR3 UART_MDR3 UART_MDR3 UART_MDR3 UART_MDR3 UART_MDR3

0x084 UART_TX_DM UART_TX_DMA UART_TX_DMA_TH UART_TX_DMA_ UART_TX_DMA_T UART_TX_DM

A_THRESHOL _THRESHOLD RESHOLD THRESHOLD HRESHOLD A_THRESHOL

D D

(1)

MSR_SPR mode is active (see Section 19.3.7.1.2, Register Access Submode)

(2)

TCR_TLR mode is active (see Section 19.3.7.1.2, Register Access Submode)

(3)

XOFF mode is active (see Section 19.3.7.1.2, Register Access Submode)

19.3.7.2 UART/IrDA (SIR, MIR, FIR)/CIR Mode Selection

To select a mode, set the UARTi.UART_MDR1[2:0] MODESELECT bit field (see Table 19-21).

3469

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...