www.ti.com

Enhanced PWM (ePWM) Module

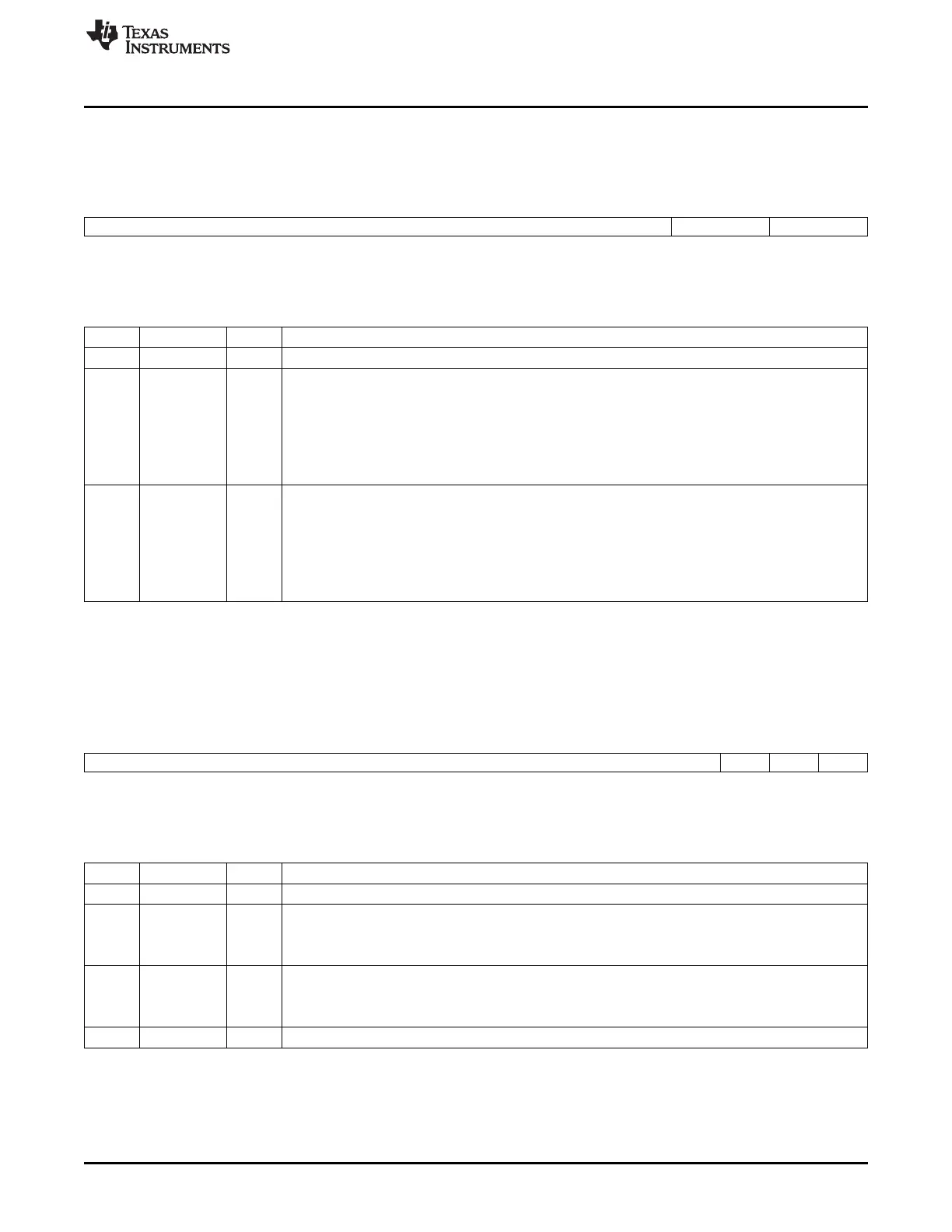

15.2.4.5.2 Trip-Zone Control Register (TZCTL)

The trip-zone control register (TZCTL) is shown in Figure 15-86 and described in Table 15-80.

Figure 15-86. Trip-Zone Control Register (TZCTL)

15 4 3 2 1 0

Reserved TZB TZA

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 15-80. Trip-Zone Control Register (TZCTL) Field Descriptions

Bits Name Value Description

15–4 Reserved 0 Reserved

3–2 TZB 0-3h When a trip event occurs the following action is taken on output EPWMxB. Which trip-zone pins can

cause an event is defined in the TZSEL register (Section 15.2.4.5.1).

0 High impedance (EPWMxB = High-impedance state)

1h Force EPWMxB to a high state

2h Force EPWMxB to a low state

3h Do nothing, no action is taken on EPWMxB.

1–0 TZA 0-3h When a trip event occurs the following action is taken on output EPWMxA. Which trip-zone pins can

cause an event is defined in the TZSEL register (Section 15.2.4.5.1).

0 High impedance (EPWMxA = High-impedance state)

1h Force EPWMxA to a high state

2h Force EPWMxA to a low state

3h Do nothing, no action is taken on EPWMxA.

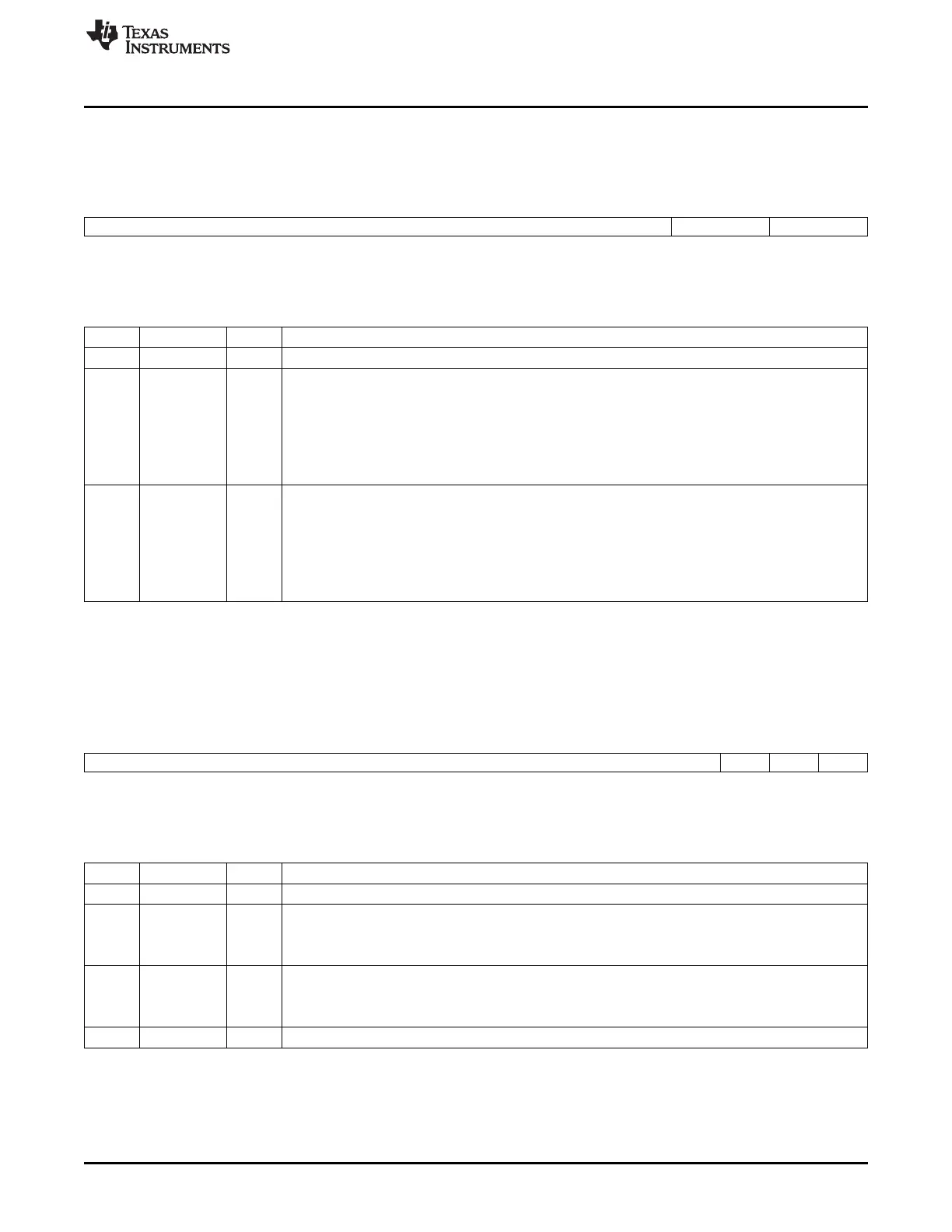

15.2.4.5.3 Trip-Zone Enable Interrupt Register (TZEINT)

The trip-zone enable interrupt register (TZEINT) is shown in Figure 15-87 and described in Table 15-81.

Figure 15-87. Trip-Zone Enable Interrupt Register (TZEINT)

15 3 2 1 0

Reserved OST CBC Rsvd

R-0 R/W-0 R/W-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 15-81. Trip-Zone Enable Interrupt Register (TZEINT) Field Descriptions

Bits Name Value Description

15-3 Reserved 0 Reserved

2 OST Trip-zone One-Shot Interrupt Enable

0 Disable one-shot interrupt generation

1 Enable Interrupt generation; a one-shot trip event will cause a EPWMxTZINT interrupt.

1 CBC Trip-zone Cycle-by-Cycle Interrupt Enable

0 Disable cycle-by-cycle interrupt generation.

1 Enable interrupt generation; a cycle-by-cycle trip event will cause an EPWMxTZINT interrupt.

0 Reserved 0 Reserved

1597

SPRUH73H–October 2011–Revised April 2013 Pulse-Width Modulation Subsystem (PWMSS)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...