McASP Registers

www.ti.com

22.4.1.6 Pin Data Input Register (PDIN)

The pin data input register (PDIN) holds the I/O pin state of each of the McASP pins. PDIN allows the

actual value of the pin to be read, regardless of the state of PFUNC and PDIR. The value after reset for

registers 1 through 15 and 24 through 31 depends on how the pins are being driven. The PDIN is shown

in Figure 22-44 and described in Table 22-17.

CAUTION

Writing to Reserved Bits

Writing a value other than 0 to reserved bits in this register may cause improper

device operation.

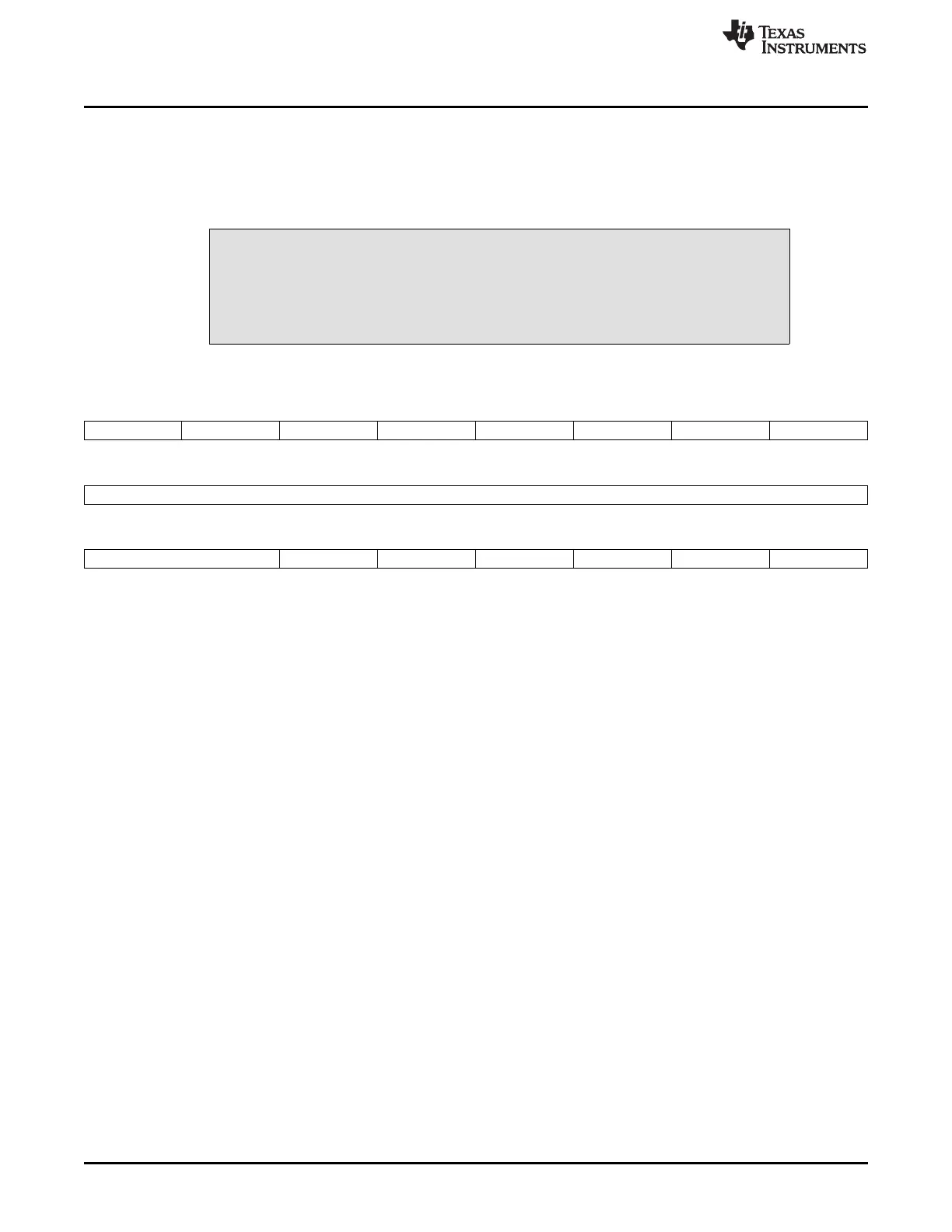

Figure 22-44. Pin Data Input Register (PDIN)

31 30 29 28 27 26 25 24

AFSR AHCLKR ACLKR AFSX AHCLKX ACLKX AMUTE Reserved

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0

23 8

Reserved

R-0

7 6 5 4 3 2 1 0

Reserved AXR5 AXR4 AXR3 AXR2 AXR1 AXR0

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

3836

Multichannel Audio Serial Port (McASP) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...