www.ti.com

GPMC

7.1.5.1 GPMC_REVISION

This register contains the IP revision code.

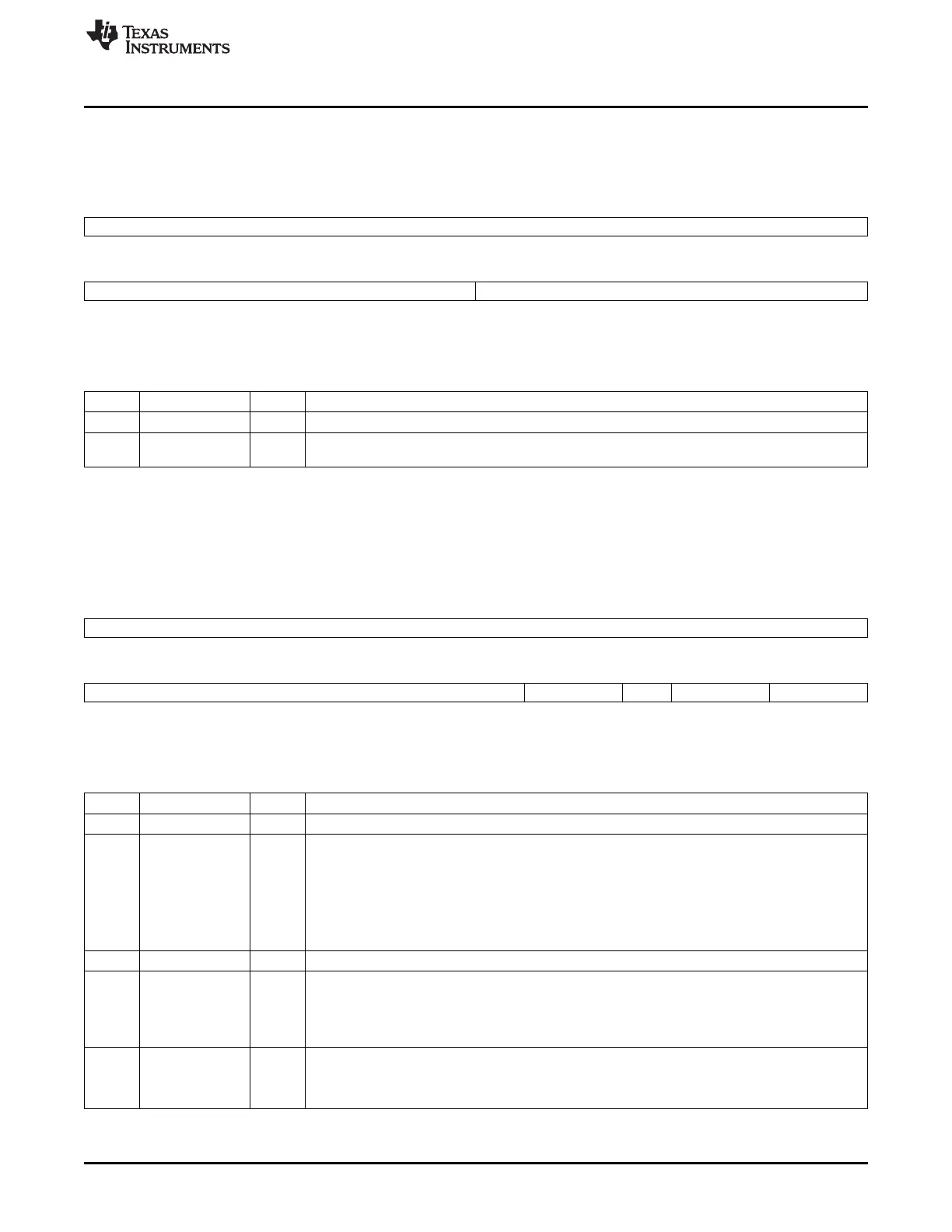

Figure 7-51. GPMC_REVISION

31 16

Reserved

R-0

15 8 7 0

Reserved REV

R-0 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-55. GPMC_REVISION Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved

7-0 REV 0-FFh IP revision. Major revision is [7-4]. Minor revision is [3-0].

Examples: 10h for revision 1.0, 21h for revision 2.1.

7.1.5.2 GPMC_SYSCONFIG

This register controls the various parameters of the OCP interface.

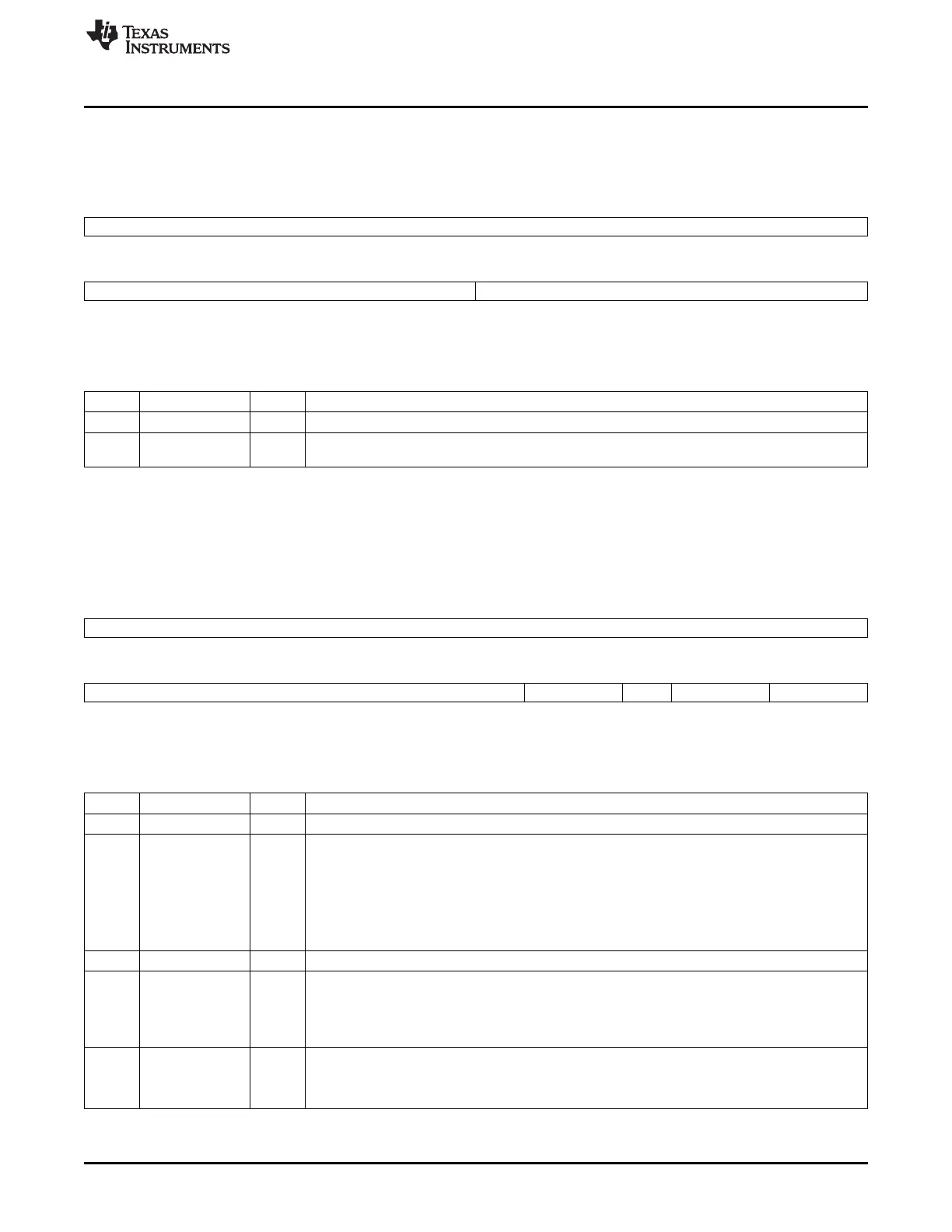

Figure 7-52. GPMC_SYSCONFIG

31 16

Reserved

R-0

15 5 4 3 2 1 0

Reserved SIDLEMODE Rsvd SOFTRESET AUTOIDLE

R-0 R/W R-0 R/W R/W

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7-56. GPMC_SYSCONFIG Field Descriptions

Bit Field Value Description

31-5 Reserved 0 Reserved

4-3 SIDLEMODE Idle mode

0 Force-idle. An idle request is acknowledged unconditionally

1h No-idle. An idle request is never acknowledged

2h Smart-idle. Acknowledgement to an idle request is given based on the internal activity of the

module

3h Reserved

2 Reserved 0 Reserved

1 SOFTRESET Software reset (Set 1 to this bit triggers a module reset. This bit is automatically reset by hardware.

During reads, it always returns 0)

0 Normal mode

1 The module is reset

0 AUTOIDLE Internal OCP clock gating strategy

0 Interface clock is free-running

1 Reserved

367

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...