www.ti.com

EDMA3 Registers

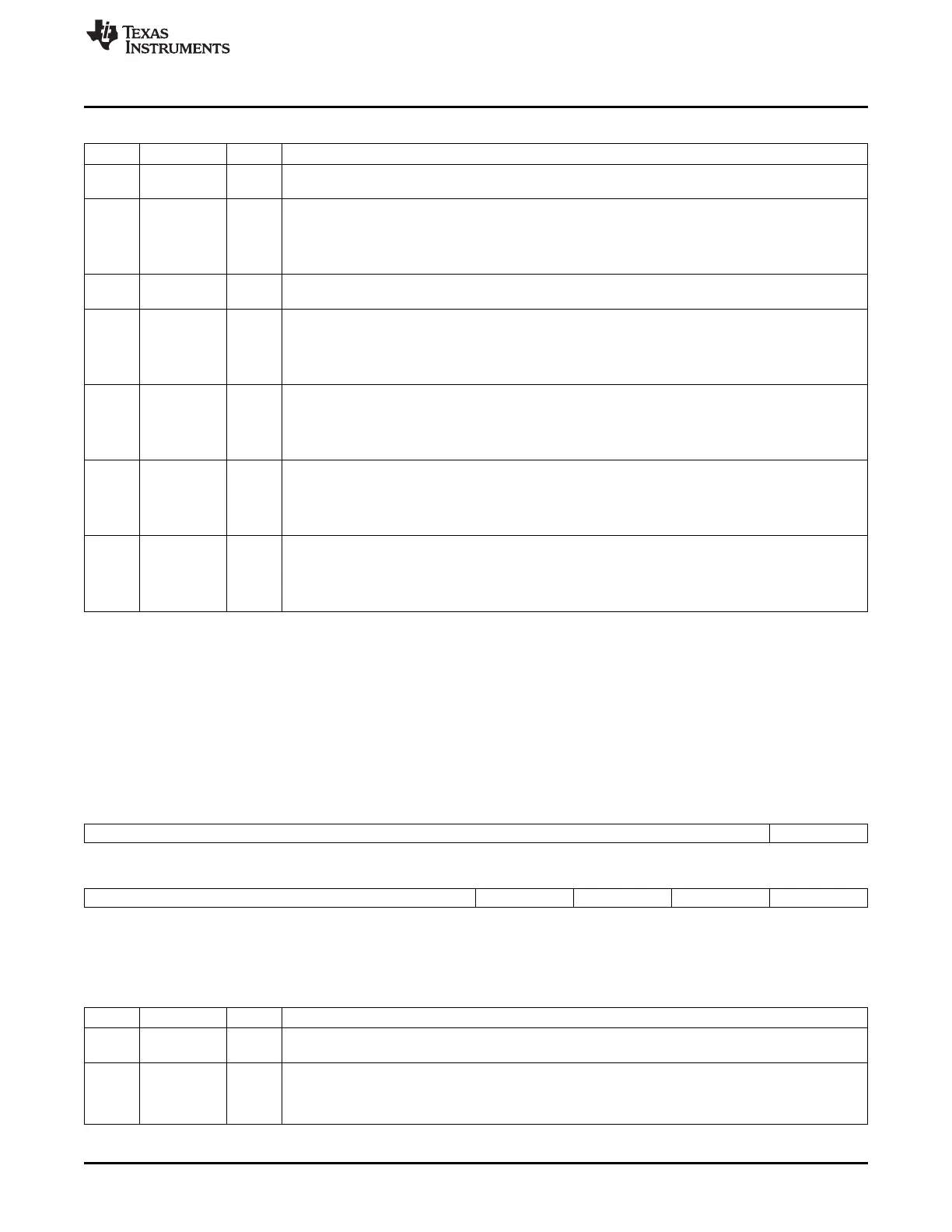

Table 11-41. EDMA3CC Error Register (CCERR) Field Descriptions

Bit Field Value Description

31-17 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

16 TCCERR Transfer completion code error. TCCERR is cleared by writing a 1 to the corresponding bit in the

EDMA3CC error clear register (CCERRCLR).

0 Total number of allowed TCCs outstanding has not been reached.

1 Total number of allowed TCCs has been reached.

15-4 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

3 QTHRXCD3 Queue threshold error for queue 3. QTHRXCD3 is cleared by writing a 1 to the corresponding bit in the

EDMA3CC error clear register (CCERRCLR).

0 Watermark/threshold has not been exceeded.

1 Watermark/threshold has been exceeded.

2 QTHRXCD2 Queue threshold error for queue 2. QTHRXCD2 is cleared by writing a 1 to the corresponding bit in the

EDMA3CC error clear register (CCERRCLR).

0 Watermark/threshold has not been exceeded.

1 Watermark/threshold has been exceeded.

1 QTHRXCD1 Queue threshold error for queue 1 . QTHRXCD1 is cleared by writing a 1 to the corresponding bit in the

EDMA3CC error clear register (CCERRCLR).

0 Watermark/threshold has not been exceeded.

1 Watermark/threshold has been exceeded.

0 QTHRXCD0 Queue threshold error for queue 0. QTHRXCD0 is cleared by writing a 1 to the corresponding bit in the

EDMA3CC error clear register (CCERRCLR).

0 Watermark/threshold has not been exceeded.

1 Watermark/threshold has been exceeded.

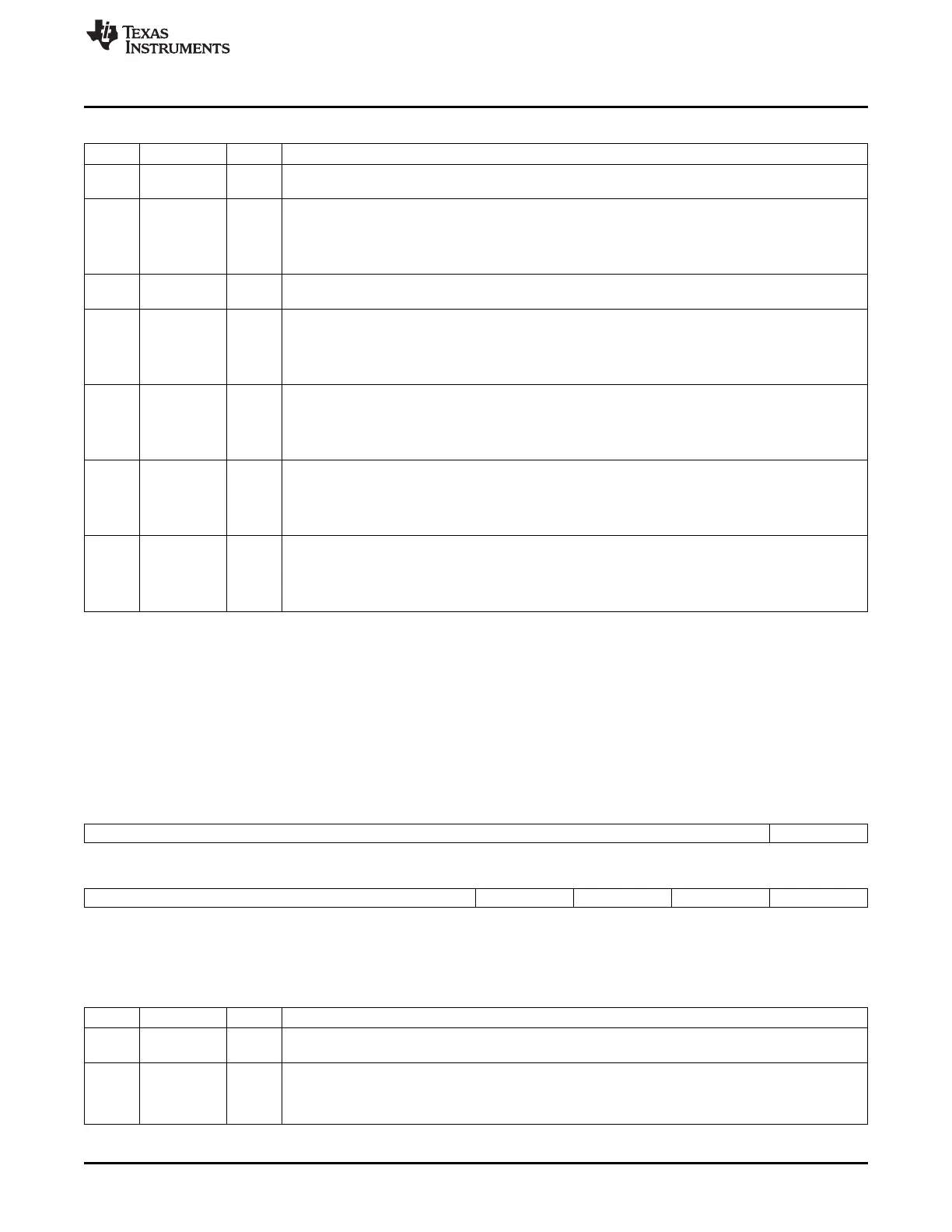

11.4.1.2.6 EDMA3CC Error Clear Register (CCERRCLR)

The EDMA3CC error clear register (CCERRCLR) is used to clear any error bits that are set in the

EDMA3CC error register (CCERR). In addition, CCERRCLR also clears the values of some bit fields in

the queue status registers (QSTATn) associated with a particular event queue. Writing a 1 to any of the

bits clears the corresponding bit in CCERR; writing a 0 has no effect.

The CCERRCLR is shown in Figure 11-57 and described in Table 11-42.

Figure 11-57. EDMA3CC Error Clear Register (CCERRCLR)

31 17 16

Reserved TCCERR

W-0 W-0

15 4 3 2 1 0

Reserved QTHRXCD3 QTHRXCD2 QTHRXCD1 QTHRXCD0

W-0 W-0 W-0 W-0 W-0

LEGEND: W = Write only; -n = value after reset

Table 11-42. EDMA3CC Error Clear Register (CCERRCLR) Field Descriptions

Bit Field Value Description

31-17 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

16 TCCERR Transfer completion code error clear.

0 No effect.

1 Clears the TCCERR bit in the EDMA3CC error register (CCERR).

955

SPRUH73H–October 2011–Revised April 2013 Enhanced Direct Memory Access (EDMA)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...