EDMA3 Registers

www.ti.com

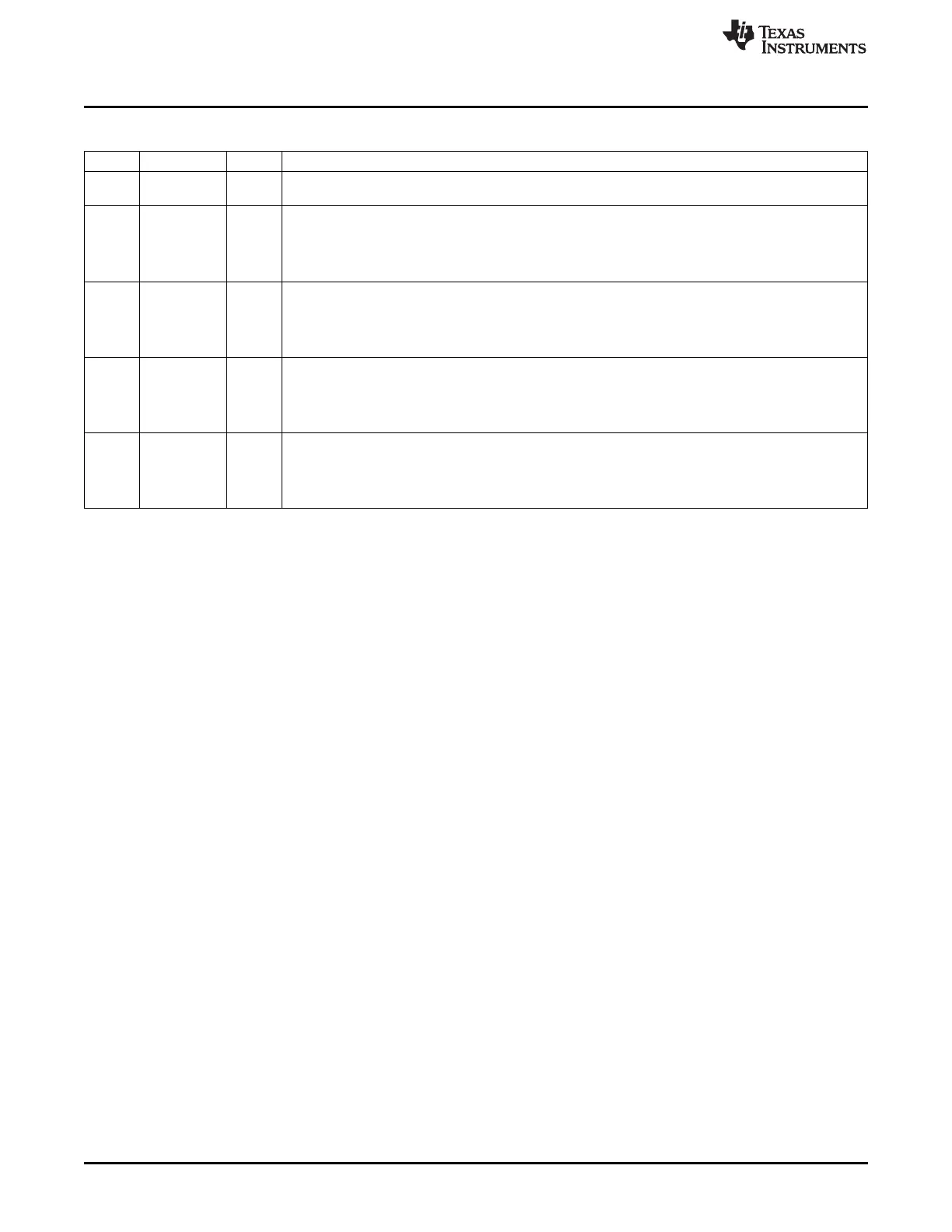

Table 11-42. EDMA3CC Error Clear Register (CCERRCLR) Field Descriptions (continued)

Bit Field Value Description

15-4 Reserved 0 Reserved. Always write 0 to this bit; writes of 1 to this bit are not supported and attempts to do so may

result in undefined behavior.

3 QTHRXCD3 Queue threshold error clear for queue 3.

0 No effect.

1 Clears the QTHRXCD3 bit in the EDMA3CC error register (CCERR) and the WM and THRXCD bits in

the queue status register 3 (QSTAT3).

2 QTHRXCD2 Queue threshold error clear for queue 2.

0 No effect.

1 Clears the QTHRXCD2 bit in the EDMA3CC error register (CCERR) and the WM and THRXCD bits in

the queue status register 2 (QSTAT2).

1 QTHRXCD1 Queue threshold error clear for queue 1.

0 No effect.

1 Clears the QTHRXCD1 bit in the EDMA3CC error register (CCERR) and the WM and THRXCD bits in

the queue status register 1 (QSTAT1).

0 QTHRXCD0 Queue threshold error clear for queue 0.

0 No effect.

1 Clears the QTHRXCD0 bit in the EDMA3CC error register (CCERR) and the WM and THRXCD bits in

the queue status register 0 (QSTAT0).

956

Enhanced Direct Memory Access (EDMA) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...