McSPI Registers

www.ti.com

24.4.1.9 McSPI Channel (i) Status Register (MCSPI_CH(i)STAT)

The McSPI channel i status register register (MCSPI_CH(i)STAT) provides status information about the

McSPI channel i FIFO transmit buffer register (MCSPI_TXn) and the McSPI channel i FIFO receive buffer

register (MCSPI_RXn) of channel i. The (MCSPI_CH(i)STAT) is shown in Figure 24-34 and described in

Table 24-20.

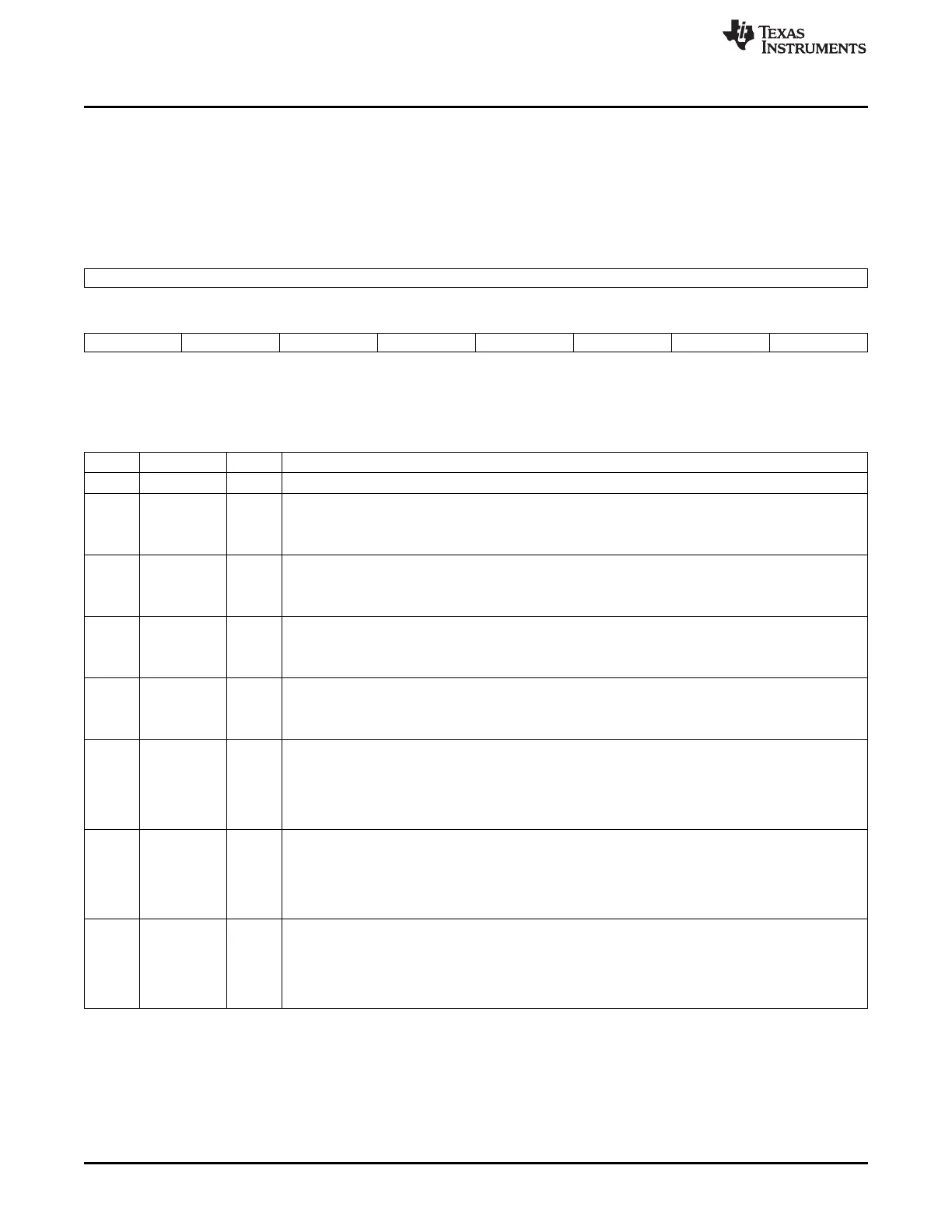

Figure 24-34. McSPI Channel (i) Status Register (MCSPI_CH(i)STAT)

31 8

Reserved

R-0

7 6 5 4 3 2 1 0

Reserved RXFFF RXFFE TXFFF TXFFE EOT TXS RXS

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

LEGEND: R = Read only; -n = value after reset

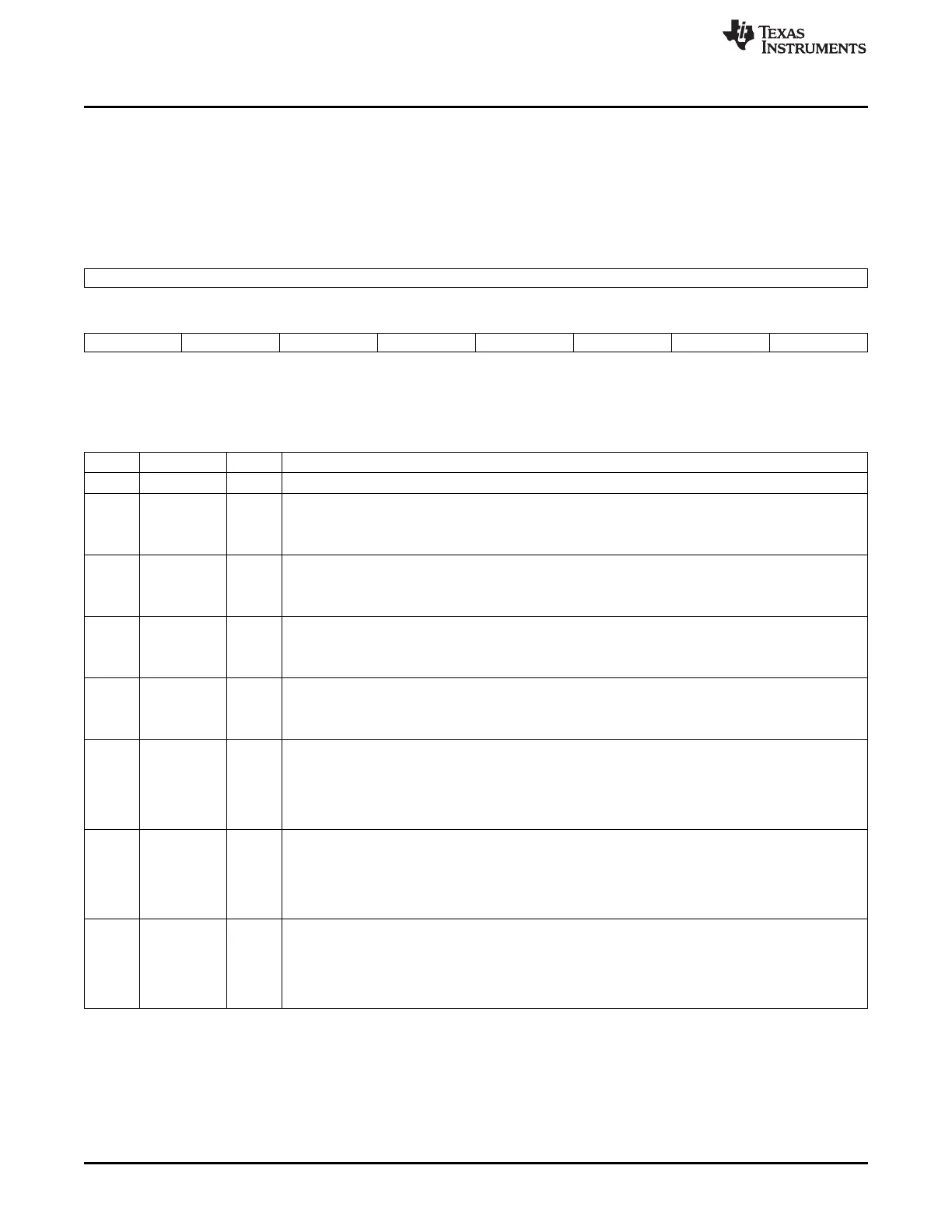

Table 24-20. McSPI Channel (i) Status Register (MCSPI_CH(i)STAT) Field Descriptions

Bit Field Value Description

31-7 Reserved 0 Read returns 0

6 RXFFF Channel i FIFO receive buffer full status.

0 FIFO receive buffer is not full.

1 FIFO receive buffer is full.

5 RXFFE Channel i FIFO receive buffer empty status.

0 FIFO receive buffer is not empty.

1 FIFO receive buffer is empty.

4 TXFFF Channel i FIFO transmit buffer full status.

0 FIFO transmit buffer is not full.

1 FIFO transmit buffer is full.

3 TXFFE Channel i FIFO transmit buffer empty status.

0 FIFO transmit buffer is not empty.

1 FIFO transmit buffer is empty.

2 EOT Channel i end-of-transfer status. The definitions of beginning and end of transfer vary with master

versus slave and the transfer format (transmit/receive mode, turbo mode).

0 This flag is automatically cleared when the shift register is loaded with the data from the transmitter

register (beginning of transfer).

1 This flag is automatically set to one at the end of an SPI transfer.

1 TXS Channel i transmitter register status. The bit is cleared when the host writes the most significant byte of

the SPI word in the MCSPI_TX(i) register. The bit is set when enabling the channel i , and also when

the SPI word is transferred from the MCSPI_TX(i) register to the shift register.

0 Register is full.

1 Register is empty.

0 RXS Channel i receiver register status. The bit is cleared when enabling the channel i, and also when the

host reads the most significant byte of the received SPI word from the MCSPI_RX(i) register. The bit is

set when the received SPI word is transferred from the shift register to the MCSPI_RX(i) register.

0 Register is empty.

1 Register is full.

4050

Multichannel Serial Port Interface (McSPI) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...