www.ti.com

UART Registers

19.5.1.25 BOF Control Register (BLR)

The BLR[6] bit is used to select whether C0h or FFh start patterns are to be used, when multiple start

flags are required in SIR mode. If only one start flag is required, this is always C0h. If n start flags are

required, either (n – 1) C0h or (n –1) FFh flags are sent, followed by a single C0h flag (immediately

preceding the first data byte). The BOF control register (BLR) is shown in Figure 19-58 and described in

Table 19-56.

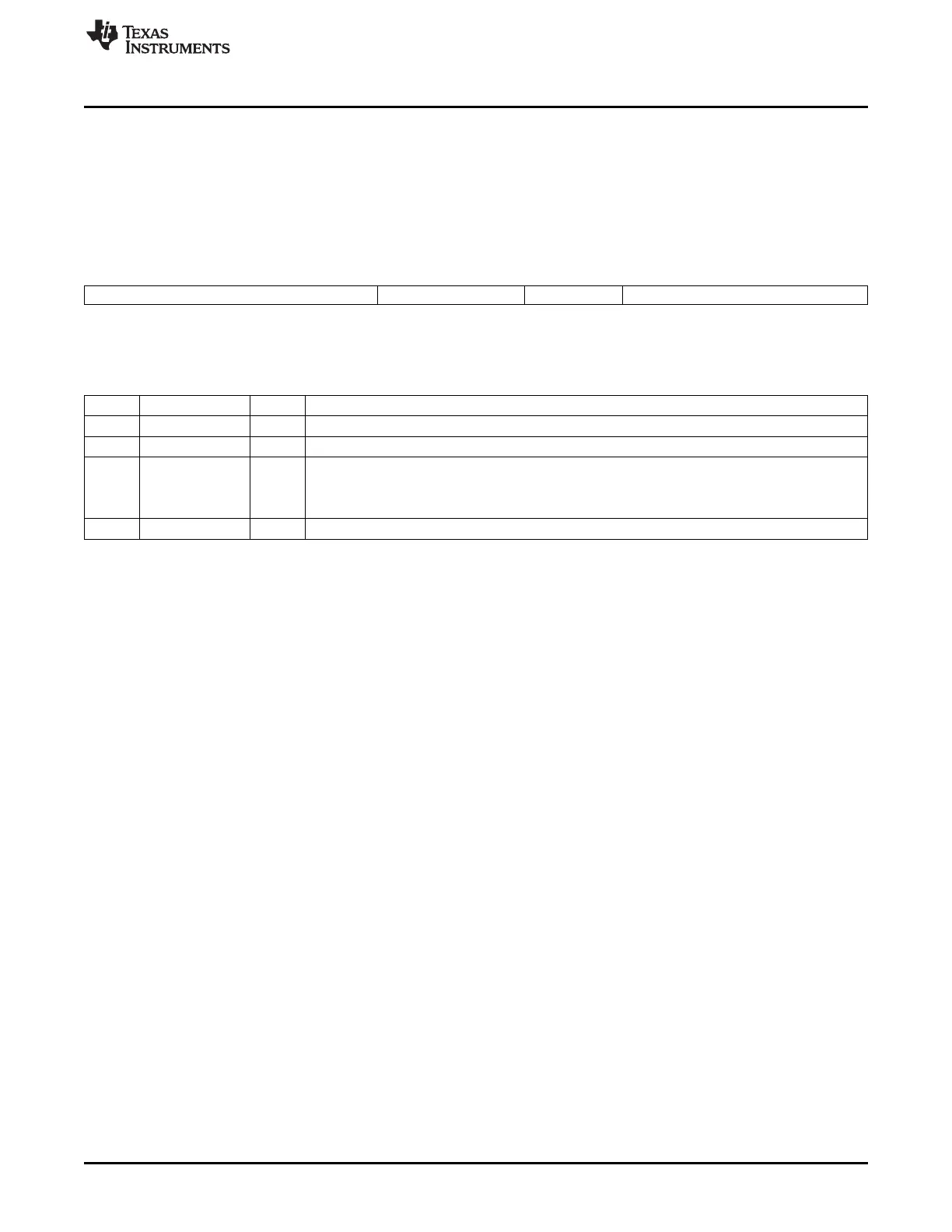

Figure 19-58. BOF Control Register (BLR)

15 8 7 6 5 0

Reserved STSFIFORESET XBOFTYPE Reserved

R-0 R/W-0 R/W-1 R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

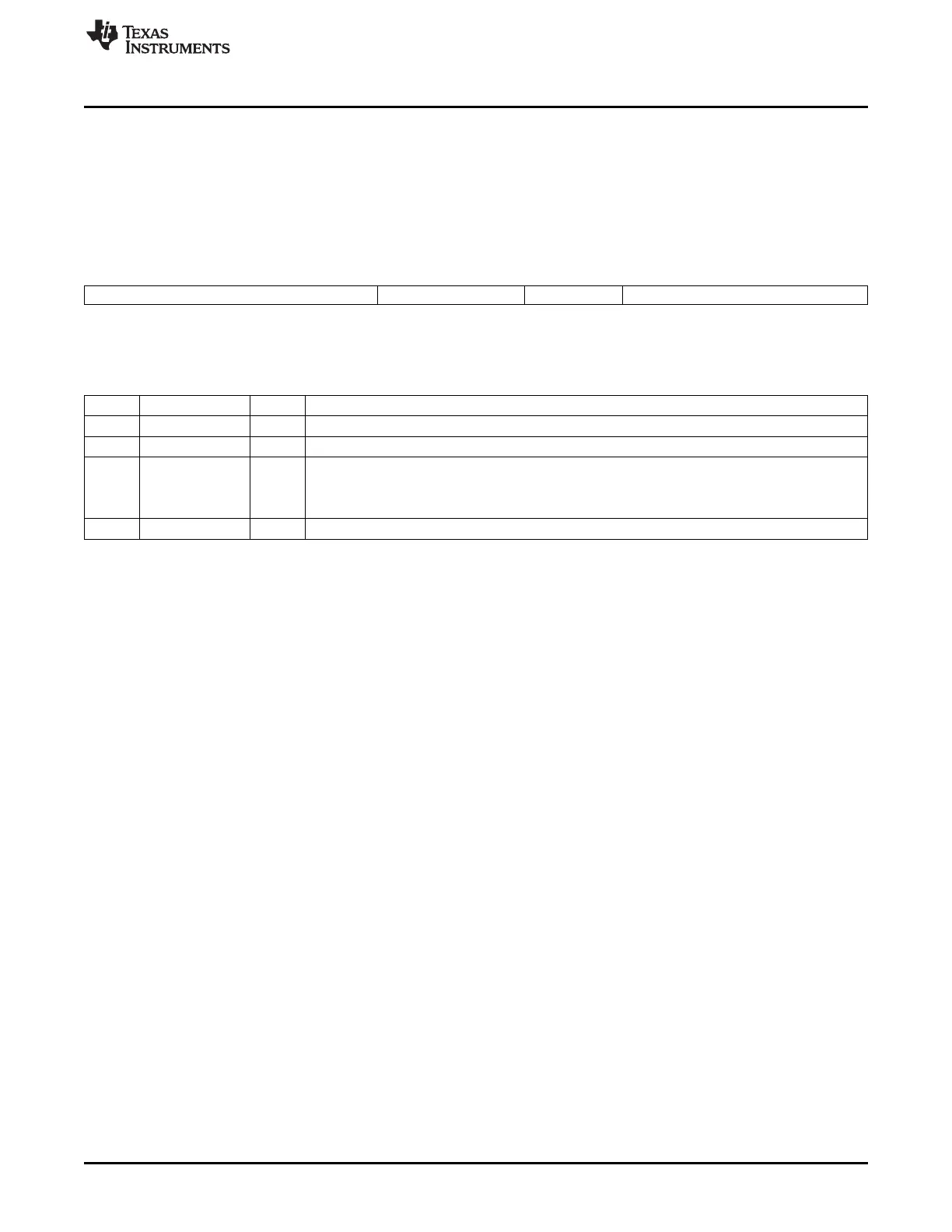

Table 19-56. BOF Control Register (BLR) Field Descriptions

Bit Field Value Description

15-8 Reserved 0 Reserved.

7 STSFIFORESET Status FIFO reset. This bit is self-clearing..

6 XBOFTYPE SIR xBOF select.

0 FFh start pattern is used.

1 C0h start pattern is used.

0 Reserved 0 Reserved.

3527

SPRUH73H–October 2011–Revised April 2013 Universal Asynchronous Receiver/Transmitter (UART)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...