Ethernet Subsystem Registers

www.ti.com

14.5.6.23 P1_TS_SEQ_MTYPE Register (offset = 11Ch) [reset = 1E0000h]

P1_TS_SEQ_MTYPE is shown in Figure 14-143 and described in Table 14-158.

CPSW PORT 1 TIME SYNC SEQUENCE ID OFFSET AND MSG TYPE.

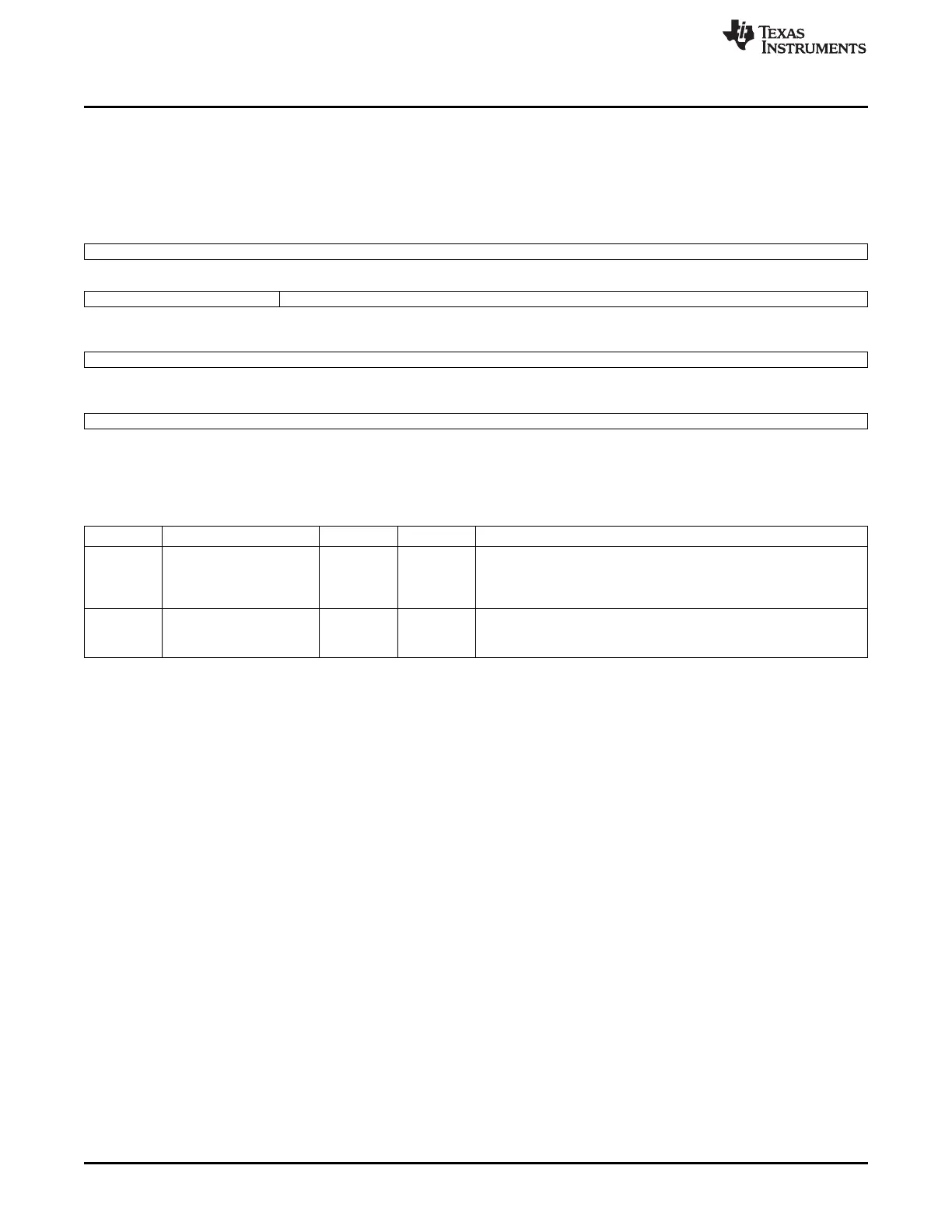

Figure 14-143. P1_TS_SEQ_MTYPE Register

31 30 29 28 27 26 25 24

Reserved

23 22 21 20 19 18 17 16

Reserved P1_TS_SEQ_ID_OFFSET

R/W-1Eh

15 14 13 12 11 10 9 8

P1_TS_MSG_TYPE_EN

R/W-0h

7 6 5 4 3 2 1 0

P1_TS_MSG_TYPE_EN

R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

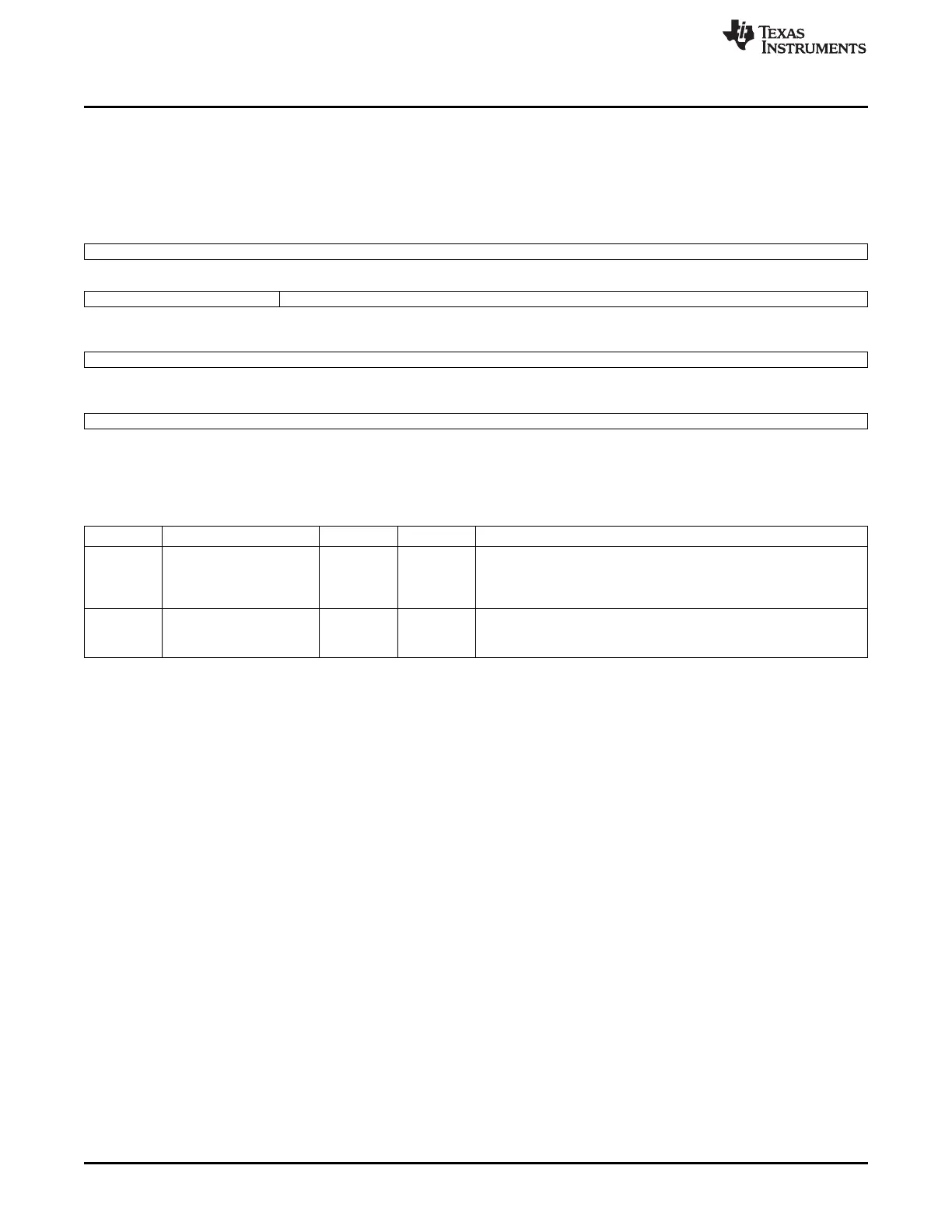

Table 14-158. P1_TS_SEQ_MTYPE Register Field Descriptions

Bit Field Type Reset Description

21-16 P1_TS_SEQ_ID_OFFSET R/W 1Eh Port 1 Time Sync Sequence ID Offset This is the number of octets

that the sequence ID is offset in the tx and rx time sync message

header.

The minimum value is 6.

15-0 P1_TS_MSG_TYPE_EN R/W 0h Port 1 Time Sync Message Type Enable - Each bit in this field

enables the corresponding message type in receive and transmit

time sync messages (Bit 0 enables message type 0 etc.).

1380

Ethernet Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...