Enhanced PWM (ePWM) Module

www.ti.com

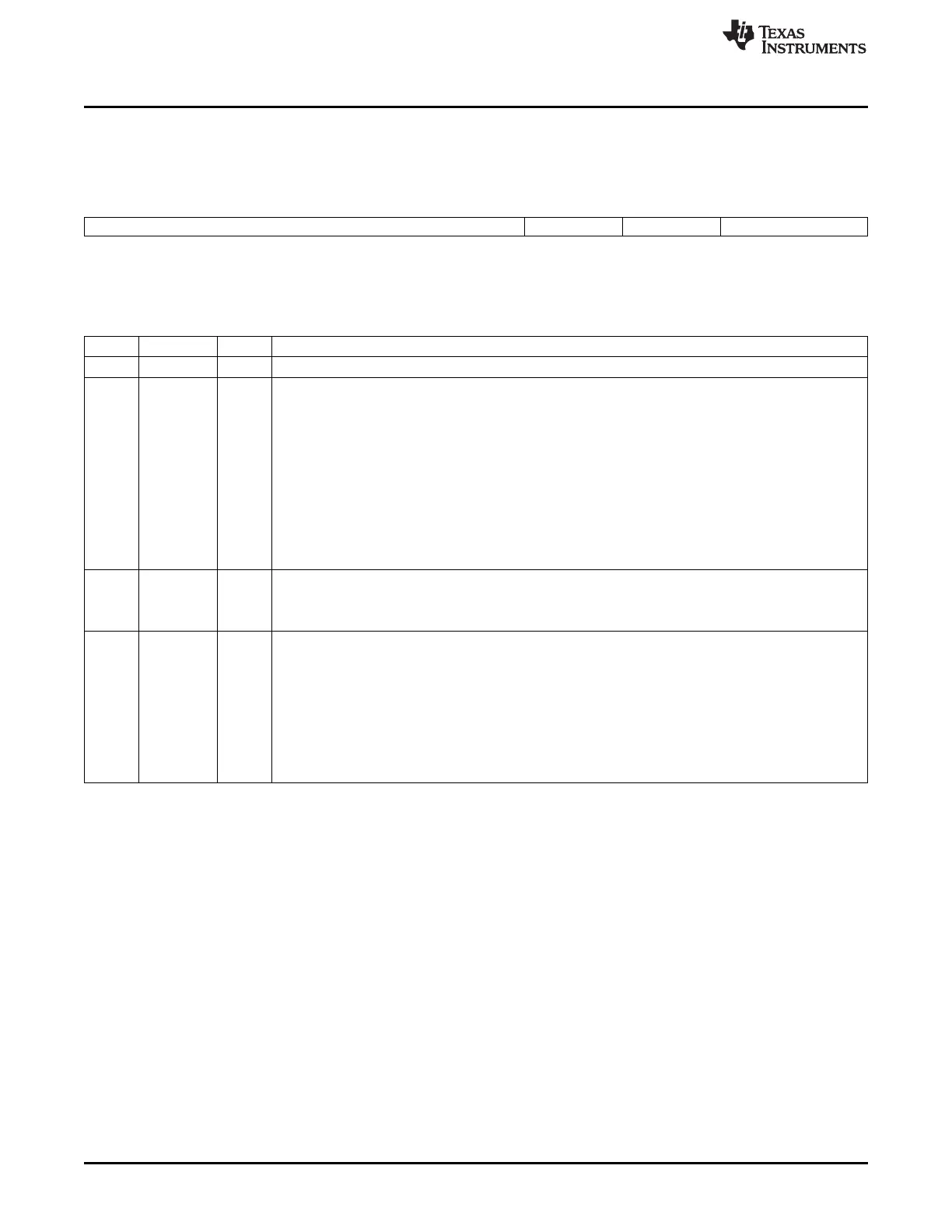

15.2.4.8.3 HRPWM Control Register (HRCTL)

The HRPWM control register (HRCTL) is shown in Figure 15-99 and described in Table 15-95.

Figure 15-99. HRPWM Control Register (HRCTL)

15 4 3 2 1 0

Reserved PULSESEL DELBUSSEL DELMODE

R-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

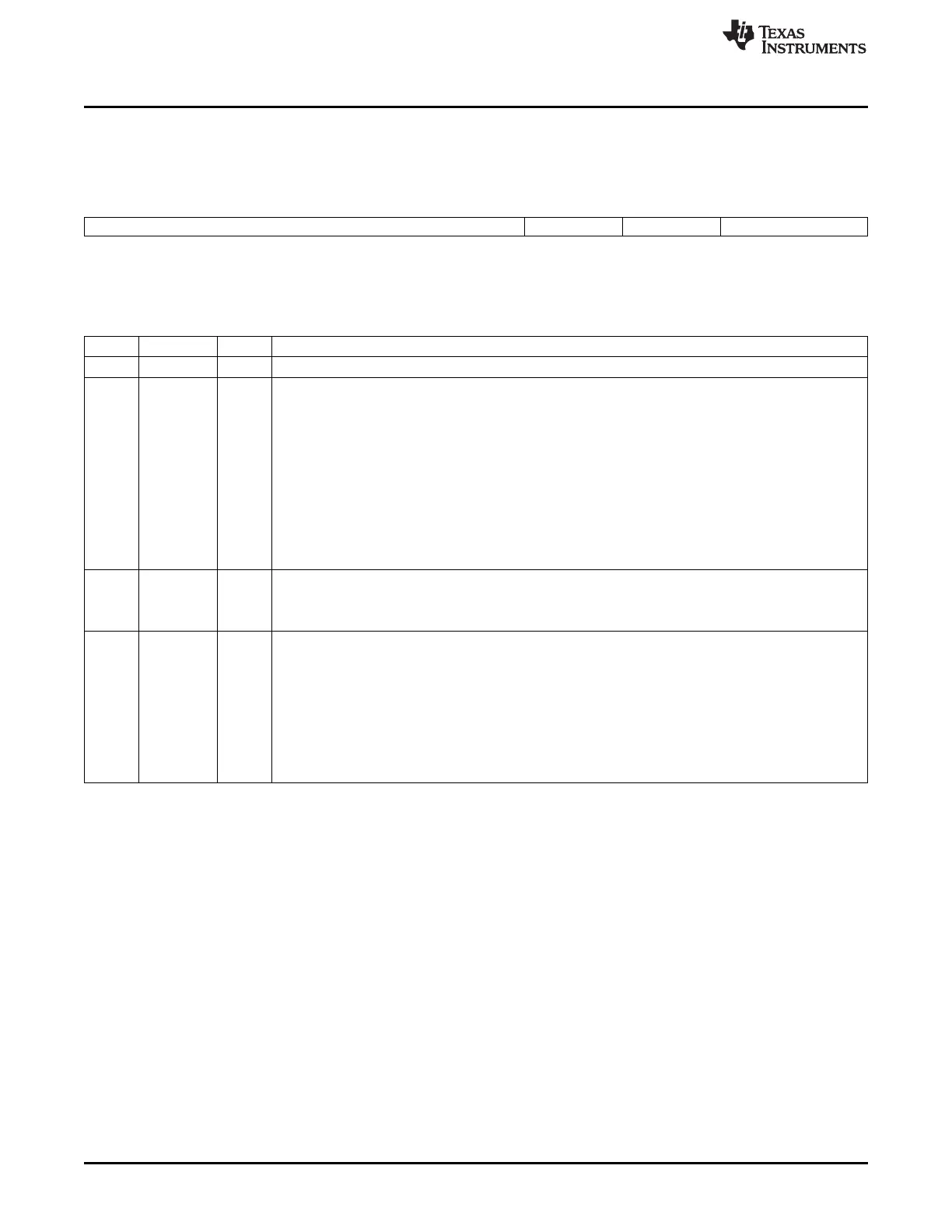

Table 15-95. HRPWM Control Register (HRCTL) Field Descriptions

Bit Field Value Description

15-4 Reserved 0 Reserved

3 PULSESEL Pulse select bits. Selects which pulse to use for timing events in the HRPWM module:

0 Select CNT_zero pulse

1 Select PRD_eq pulse

Note: The user needs to select the pulse to match the selection in the EPWM module. If TBPHSHR bus is

selected, then CNT_zero pulse should be used. If COMPAHR bus is selected, then it should match the bit

setting of the CMPCTL[LOADMODE] bits in the EPWM module as follows:

0 CNT_zero pulse

1h PRD_eq pulse

2h CNT_zero or PRD_eq (should not use with HRPWM)

3h No loads (should not use with HRPWM)

2 DELBUSSE Delay Bus Select Bit: Selects which bus is used to select the delay for the PWM pulse:

L

0 Select CMPAHR(8) bus from compare module of EPWM (default on reset).

1 Select TBPHSHR(8) bus from time base module.

1-0 DELMODE 0-3h Delay Mode Bits: Selects which edge of the PWM pulse the delay is inserted:

0 No delay inserted (default on reset)

1h Delay inserted rising edge

2h Delay inserted falling edge

3h Delay inserted on both edges

Note: When DELMODE = 0,0, the HRCALM[CALMODE] bits are ignored and the delay line is in by-pass

mode. Additionally, DLYIN is connected to CALIN and a continuous low value is fed to the delay line to

minimize activity in the module.

1606

Pulse-Width Modulation Subsystem (PWMSS) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...