www.ti.com

GPMC

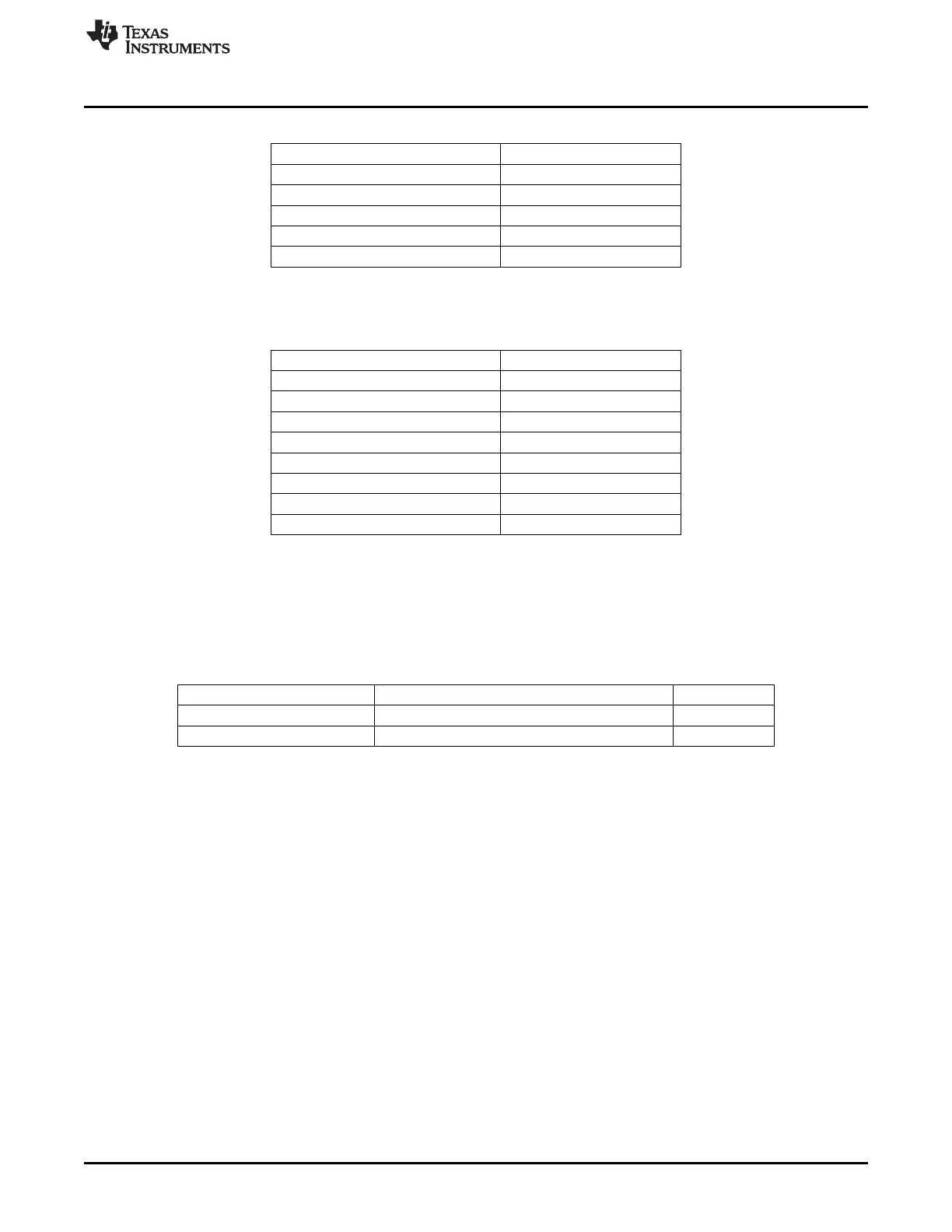

Table 7-24. GPMC Configuration in NOR Mode

Step Description

NOR Memory Type See Table 7-27

NOR Chip-Select Configuration See Table 7-28

NOR Timings Configuration See Table 7-29

Wait Pin Configuration See Table 7-30

Enable Chip-Select See Table 7-31

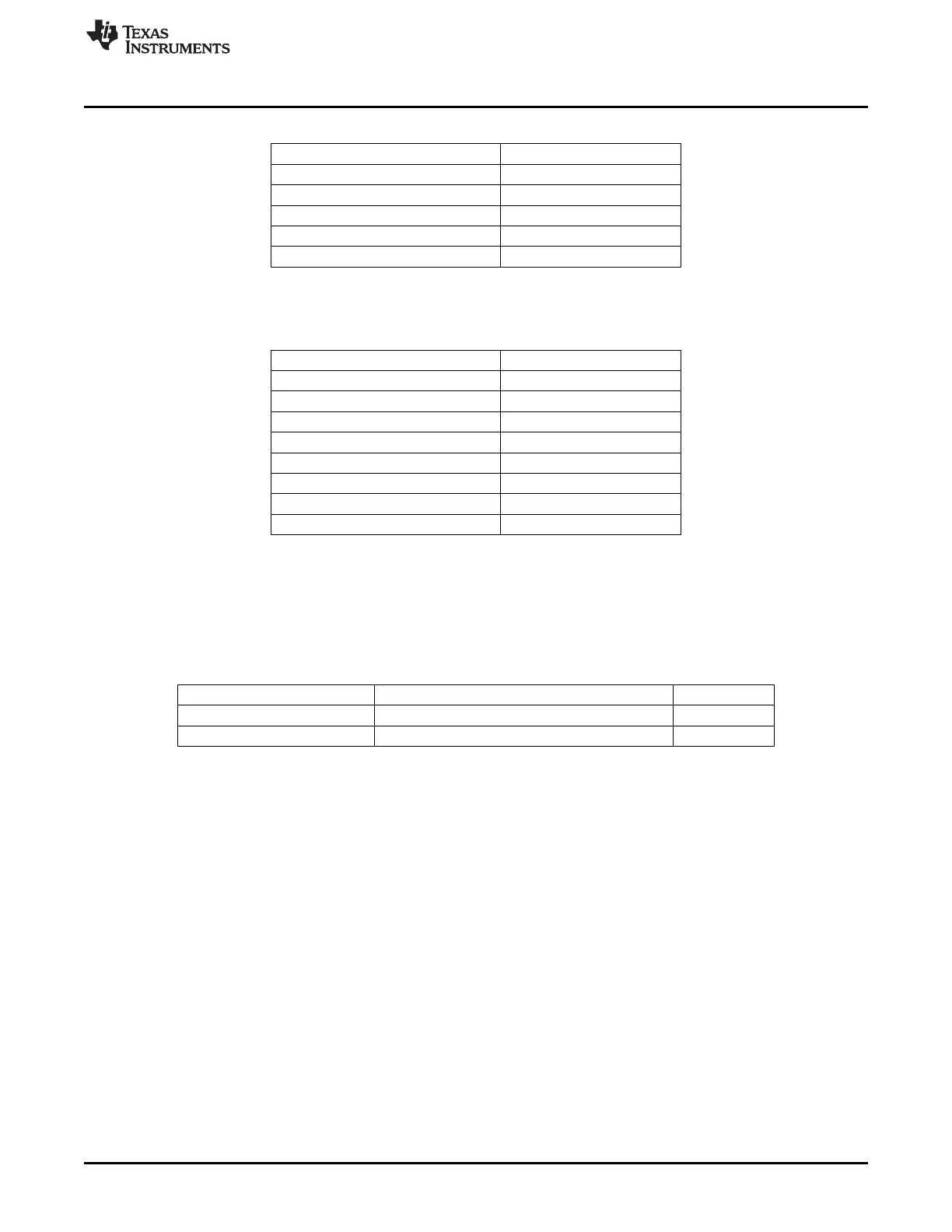

Table 7-25. GPMC Configuration in NAND Mode

Step Description

NAND Memory Type See Table 7-32

NAND Chip-Select Configuration See Table 7-33

Write Operations (Asynchronous) See Table 7-34

Read Operations (Asynchronous) See Table 7-34

ECC Engine See Table 7-35

Prefetch and Write-Posting Engine See Table 7-36

Wait Pin Configuration See Table 7-37

Enable Chip-Select See Table 7-38

7.1.3.5 GPMC Initialization

Table 7-26 describes the settings required to reset the GPMC.

Table 7-26. Reset GPMC

Sub-process Name Register / Bitfield Value

Start a software reset GPMC_SYSCONFIG[1] SOFTRESET 1

Wait until GPMC_SYSSTATUS[0] RESETDONE 1

337

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...