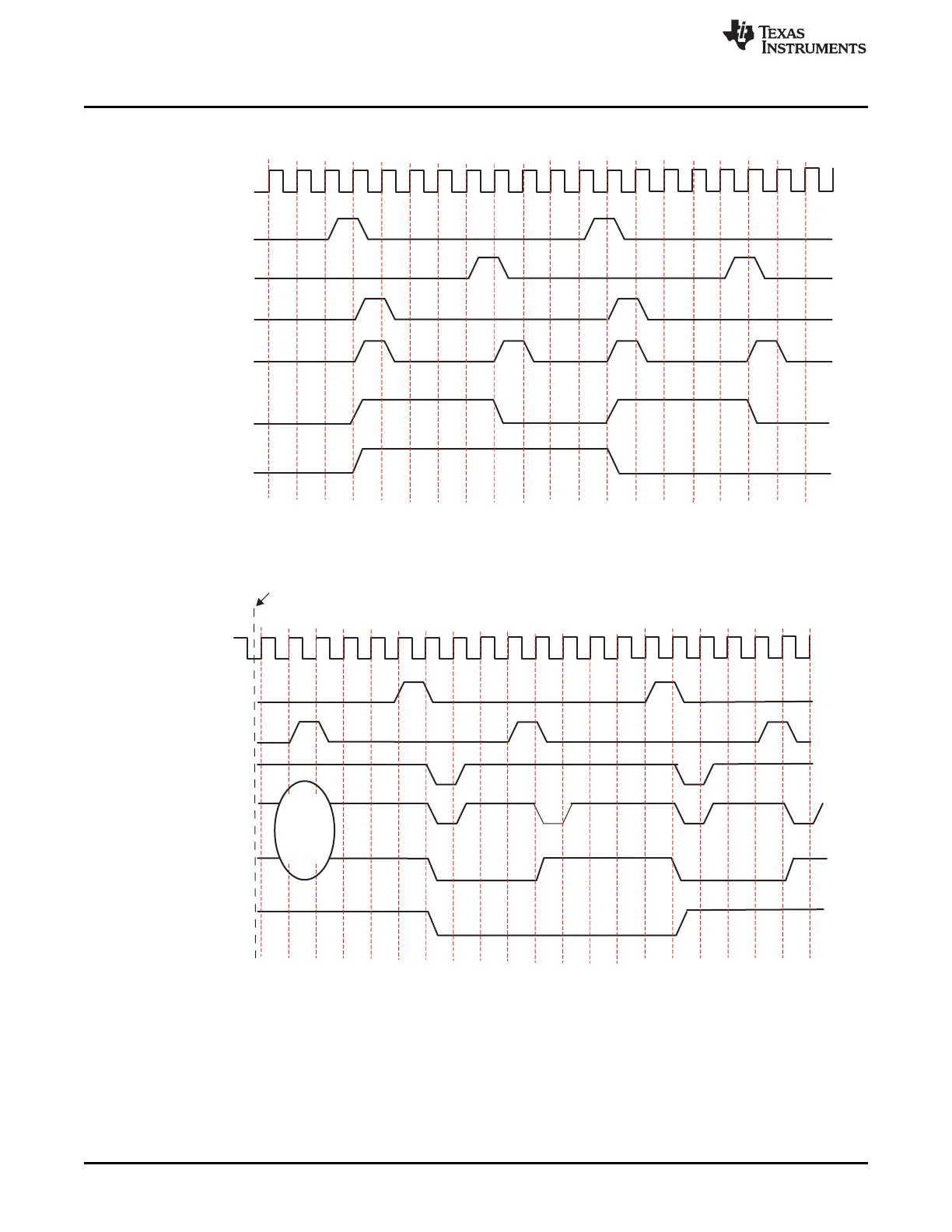

pi_timer_clk

internal

overflow pulse

match pulse

timer_pwm

(TRG = 01 & PT=0)

Set-up mode sequence

First

match

event

ignored

internal

timer_pwm

(TRG = 10 & PT=0)

timer_pwm

(TRG = 10 & PT=1)

timer_pwm

(TRG = 01 & PT=1)

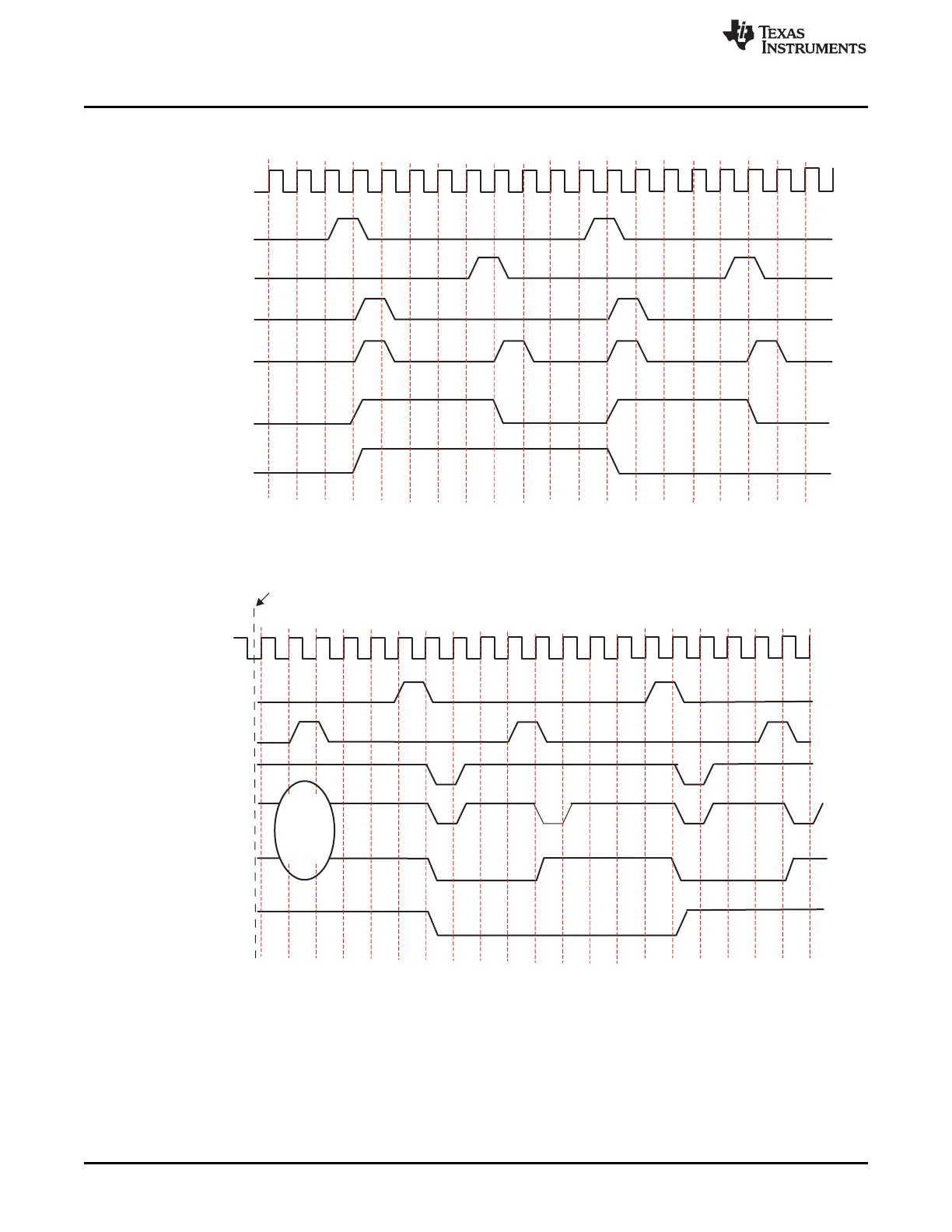

pi_timer_clk

timer_pwm (TRG = 10

& PT = 0)

timer_pwm (TRG = 01

& PT = 0)

internal

match pulse

internal

overflow pulse

timer_pwm (TRG = 10

& PT = 1)

timer_pwm (TRG = 01

& PT = 1)

DMTimer 1ms

www.ti.com

Figure 20-32. Timing Diagram of Pulse-Width Modulation, SCPWM Bit = 0

On the next wave TCLR (SCPWM bit) is set to ‘1’.

Figure 20-33. Timing Diagram of Pulse-Width Modulation, SCPWM Bit = 1

20.2.3.6 Timer Interrupt Control

The timer can issue an overflow interrupt, a timer match interrupt and a timer capture interrupt. Each

internal interrupt sources can be independently enabled/disabled in the Interrupt Enable Register TIER.

When the interrupt event has been issued the associated interrupt status bit is set in the Timer Status

Register (TISR). The pending interrupt event is reset when the set status bit is overwritten by a “1” value.

Reading the Interrupt Status Register and writing the value back allows fast acknowledge interrupt

process.

3594

Timers SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...