EMIF

www.ti.com

7.3.5.33 DDR_PHY_CTRL_1 Register (offset = E4h) [reset = 0h]

DDR_PHY_CTRL_1 is shown in Figure 7-123 and described in Table 7-143.

A write to the DDR PHY Control 1 register must be followed by a write to the SDRAM_CONFIG register to

ensure that the control update/acknowledge protocol is performed on the DID. If CAS latency = 5, the

minimum read latency = 5 + 2 = 7 and reg_read_latency must be programmed as 7 - 1 = 6. The maximum

read latency = 5 + 7 = 12 and reg_read_latency must be programmed as 12 - 1 = 11.

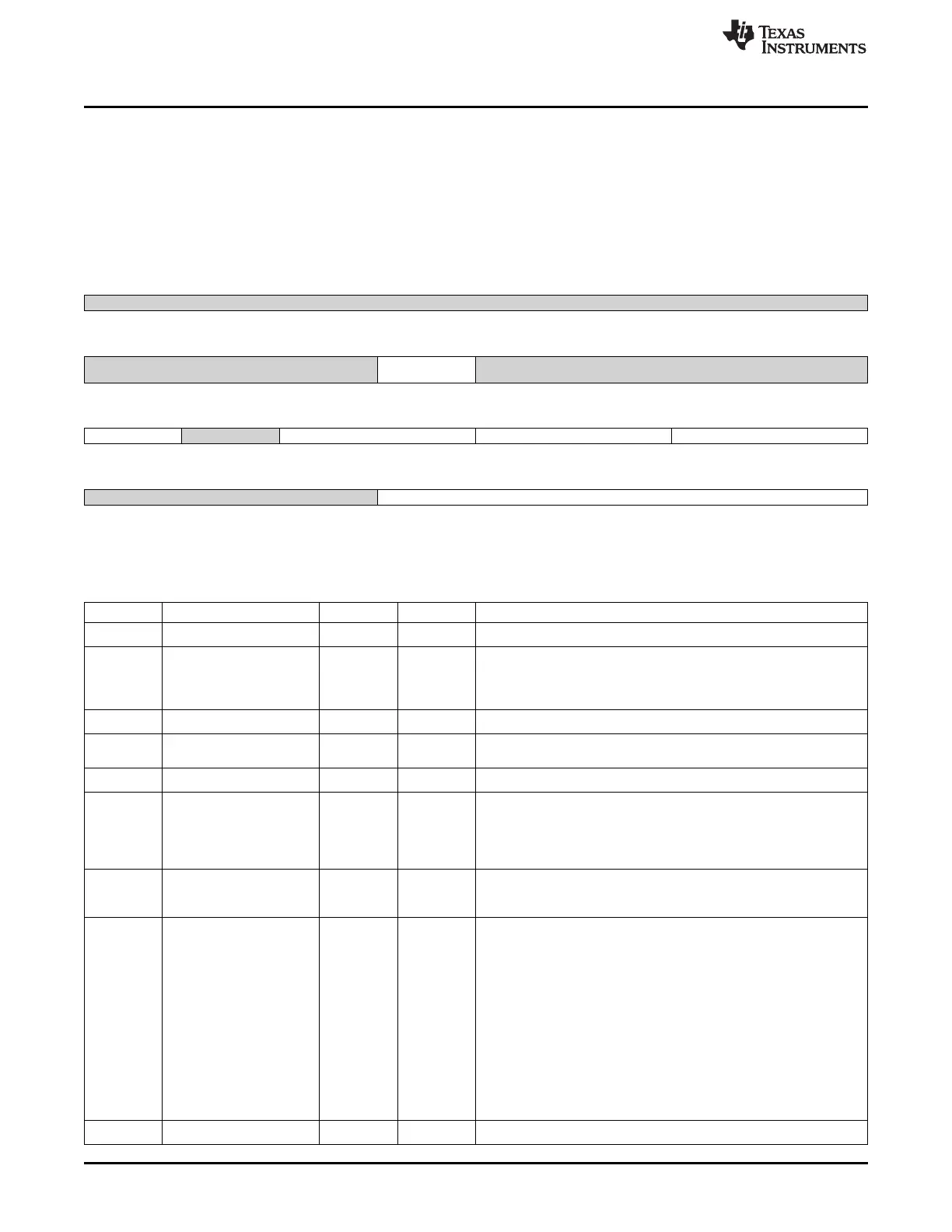

Figure 7-123. DDR_PHY_CTRL_1 Register

31 30 29 28 27 26 25 24

Reserved

R/W-0h

23 22 21 20 19 18 17 16

Reserved reg_phy_enable_dyna Reserved

mic_pwrdn

R/W-0h R/W-1h R/W-0h

15 14 13 12 11 10 9 8

reg_phy_rst_n Reserved reg_phy_idle_local_odt reg_phy_wr_local_odt reg_phy_rd_local_odt

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

7 6 5 4 3 2 1 0

Reserved reg_read_latency

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

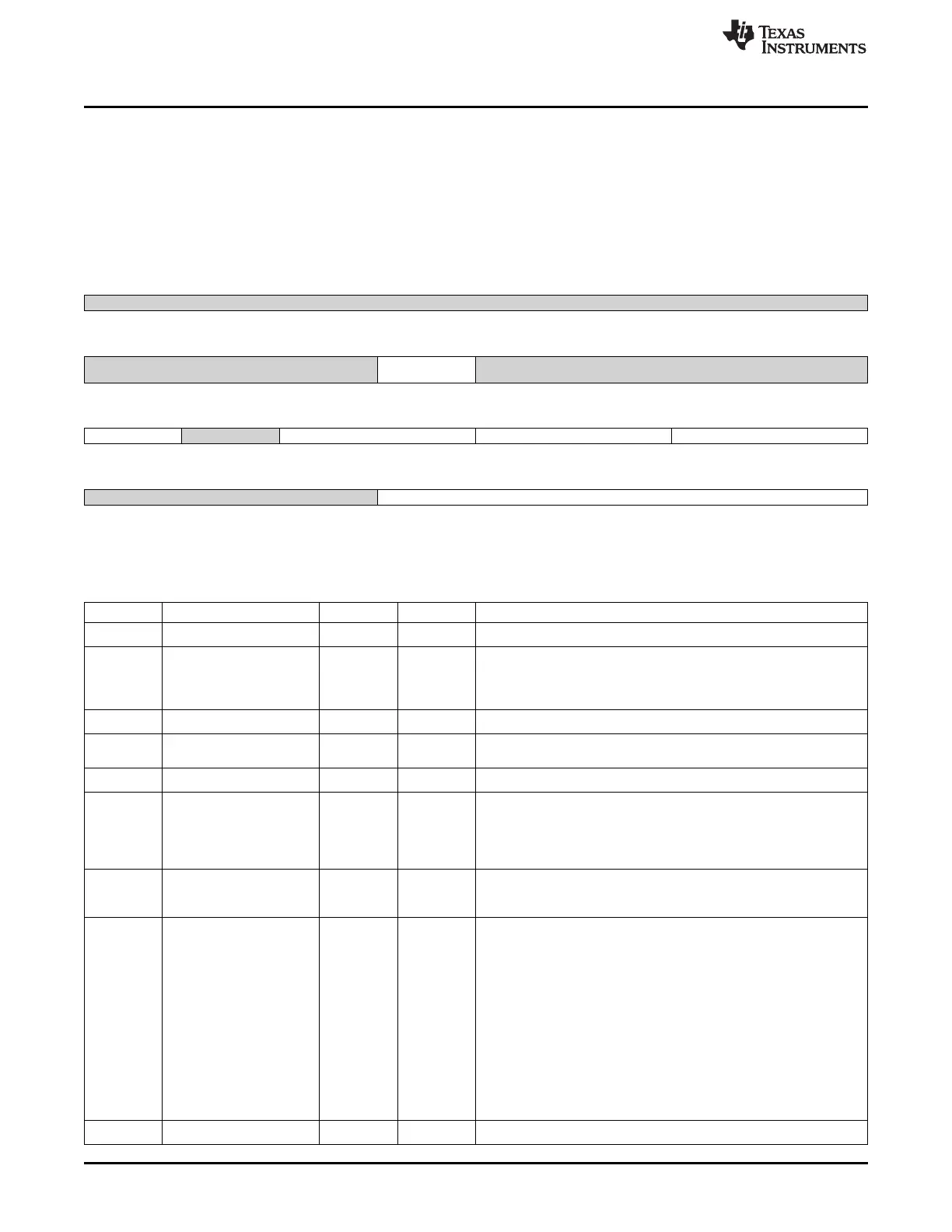

Table 7-143. DDR_PHY_CTRL_1 Register Field Descriptions

Bit Field Type Reset Description

31-21 Reserved R/W 0h

Reserved.

20 reg_phy_enable_dynamic R/W 1h Dynamically enables powering down the IO receiver when not

_pwrdn performing a read.

0 = IO receivers always powered up.

1 = IO receivers only powered up during a read.

19-16 Reserved R/W 0h

Reserved.

15 reg_phy_rst_n R/W 0h Writing a 1 to this bit will hold the PHY macros in reset.

Writing a 0 will bring PHY macros out of reset.

14 Reserved R/W 0h

Reserved.

13-12 reg_phy_idle_local_odt R/W 0h Value to drive on the 2-bit local_odt (On-Die Termination) PHY

outputs when reg_phy_dynamic_pwrdn_enable is asserted and a

read is not in progress and reg_phy_dynamic_pwrdn_enable.

Typically this is the value required to disable termination (00) to save

power when idle.

11-10 reg_phy_wr_local_odt R/W 0h This bit controls the value assigned to the reg_phy_wr_local_odt

input on the data macros.

Always set to 00.

9-8 reg_phy_rd_local_odt R/W 0h Value to drive on the 2-bit local_odt (On-Die Termination) PHY

outputs when output enable is not asserted and a read is in progress

(where in progress is defined as after a read command is issued and

until all read data has been returned all the way to the controller.)

Typically this is set to the value required to enable termination at the

desired strength for read usage.

00 = ODT off.

01 = ODT off.

10 = Full thevenin load. Effective ODT is equivalent to 1x the output

driver impedance setting in DDR_DATAx_IOCTRL.io_config_i

register bits.

11 = Half thevenin load. Effective ODT is equivalent to 2x the output

driver impedance setting in DDR_DATAx_IOCTRL.io_config_i

register bits.

7-5 Reserved R/W 0h

Reserved.

458

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...