www.ti.com

GPMC

7.1.5.4 GPMC_IRQSTATUS

This interrupt status register regroups all the status of the module internal events that can generate an

interrupt.

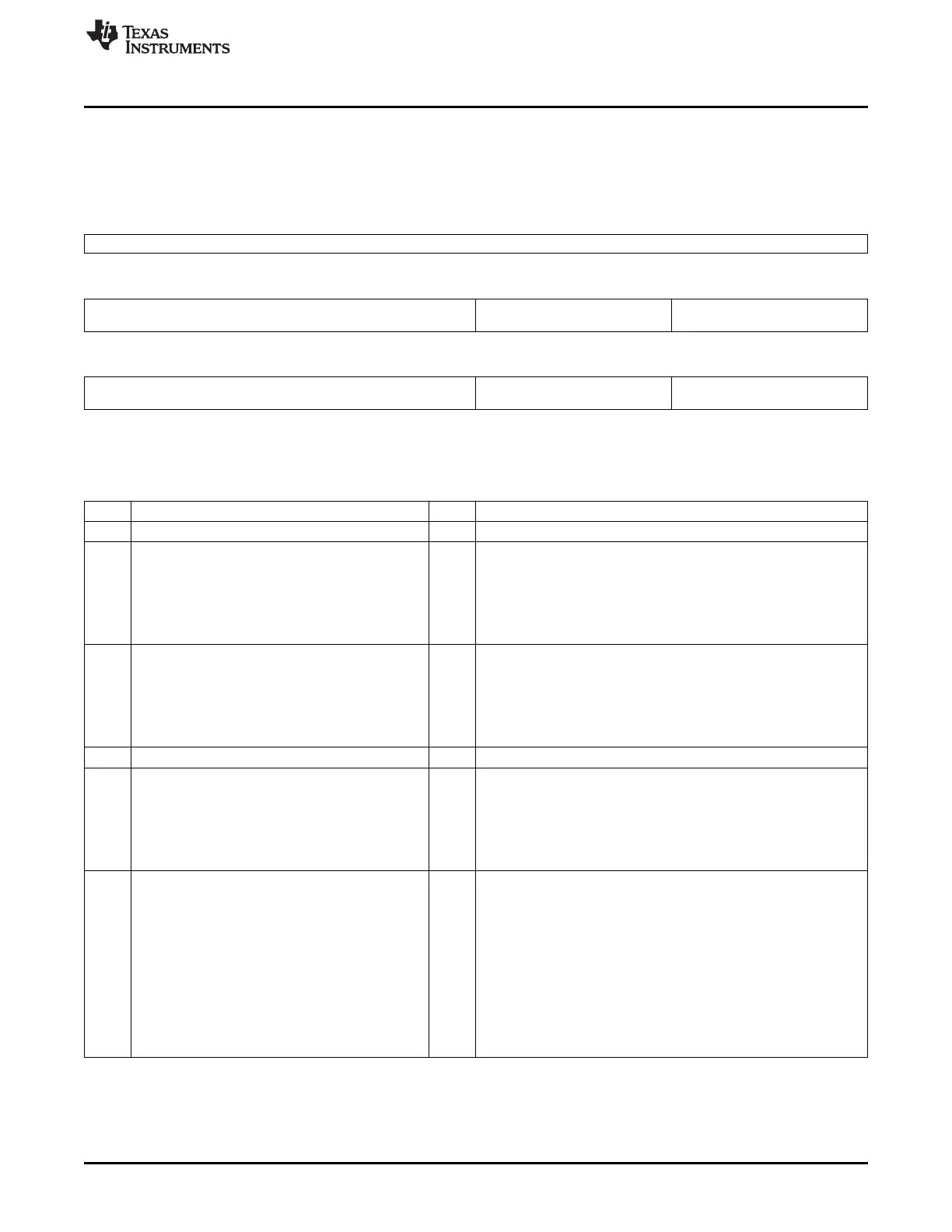

Figure 7-54. GPMC_IRQSTATUS

31 16

Reserved

R-0

15 10 9 8

Reserved WAIT1EDGE WAIT0EDGE

DETECTIONSTATUS DETECTIONSTATUS

R-0 R/W-0 R/W-0

7 2 1 0

Reserved TERMINAL FIFOEVENT

COUNTSTATUS STATUS

R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

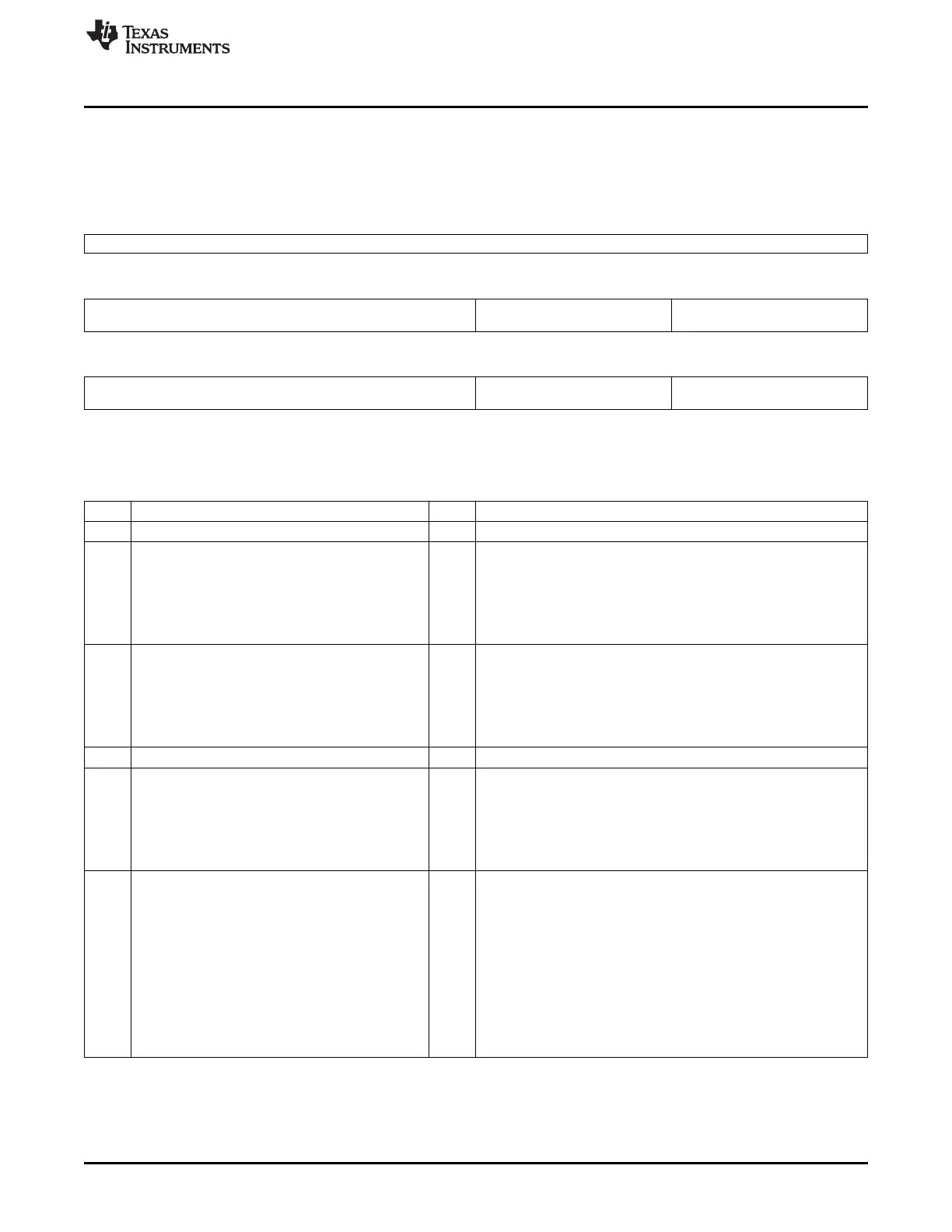

Table 7-58. GPMC_IRQSTATUS Field Descriptions

Bit Field Value Description

31-10 Reserved 0 Reserved

9 WAIT1EDGEDETECTIONSTATUS Status of the Wait1 Edge Detection interrupt

R0 A transition on WAIT1 input pin has not been detected

W0 WAIT1EDGEDETECTIONSTATUS bit unchanged

R1 A transition on WAIT1 input pin has been detected

W1 WAIT1EDGEDETECTIONSTATUS bit is reset

8 WAIT0EDGEDETECTIONSTATUS Status of the Wait0 Edge Detection interrupt

R0 A transition on WAIT0 input pin has not been detected

W0 WAIT0EDGEDETECTIONSTATUS bit unchanged

R1 A transition on WAIT0 input pin has been detected

W1 WAIT0EDGEDETECTIONSTATUS bit is reset

7-2 Reserved 0 Reserved

1 TERMINALCOUNTSTATUS Status of the TerminalCountEvent interrupt

R0 Indicates that CountValue is greater than 0

W0 TERMINALCOUNTSTATUS bit unchanged

R1 Indicates that CountValue is equal to 0

W1 TERMINALCOUNTSTATUS bit is reset

0 FIFOEVENTSTATUS Status of the FIFOEvent interrupt

R0 Indicates than less than GPMC_PREFETCH_STATUS[16]

FIFOTHRESHOLDSTATUS bytes are available in prefetch mode

and less than FIFOTHRESHOLD bytes free places are available in

write-posting mode.

W0 FIFOEVENTSTATUS bit unchanged

R1 Indicates than at least GPMC_PREFETCH_STATUS[16]

FIFOTHRESHOLDSTATUS bytes are available in prefetch mode

and at least FIFOTHRESHOLD bytes free places are available in

write-posting mode.

W1 FIFOEVENTSTATUS bit is reset

369

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...