GPMC

www.ti.com

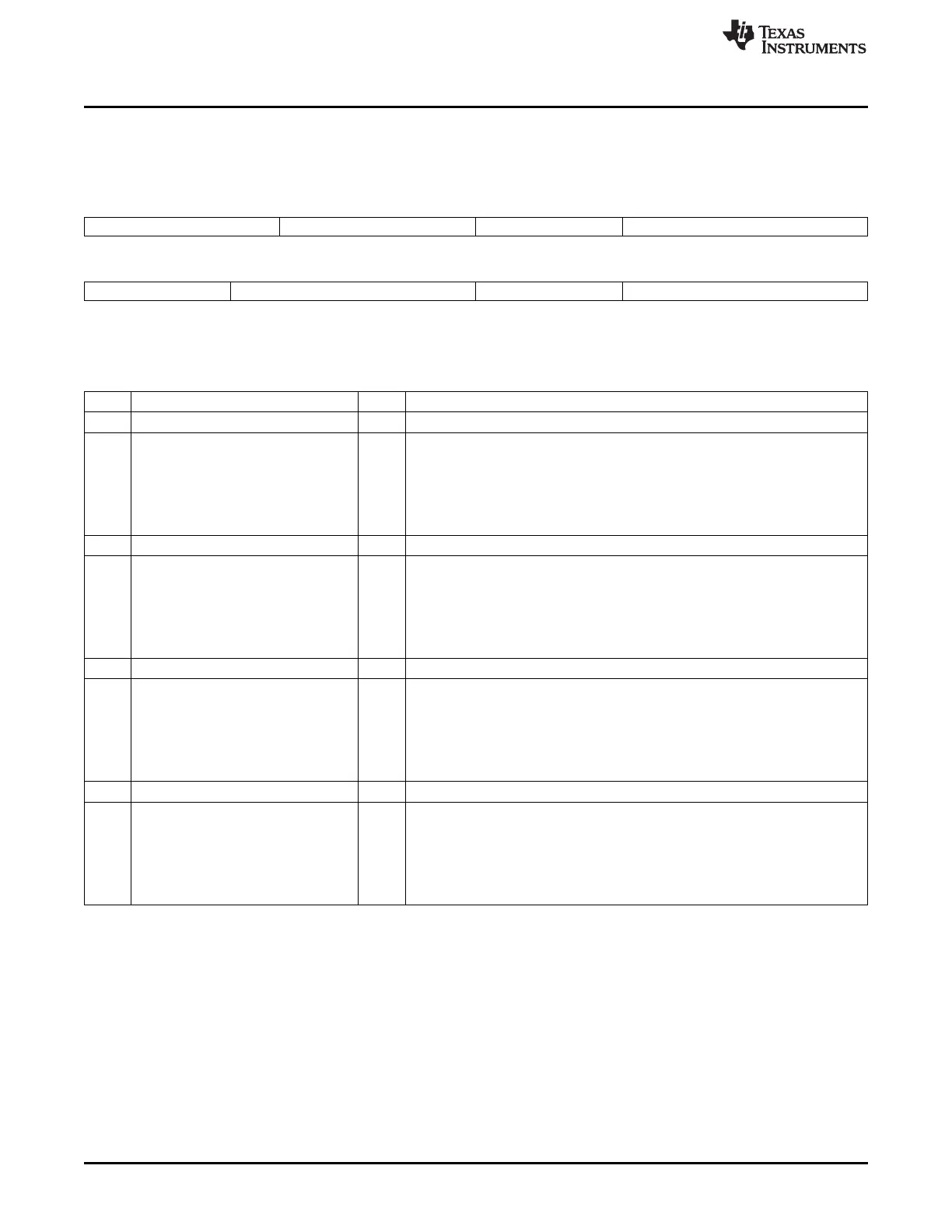

7.1.5.15 GPMC_CONFIG5_i

RdAccessTime and CycleTime timing parameters configuration.

Figure 7-65. GPMC_CONFIG5_i

31 28 27 24 23 21 20 16

Reserved PAGEBURSTACCESSTIME Reserved RDACCESSTIME

R-0 R/W-0 R-0 R/W-0

15 13 12 8 7 5 4 0

Reserved WRCYCLETIME Reserved RDCYCLETIME

R-0 R/W-0 R-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

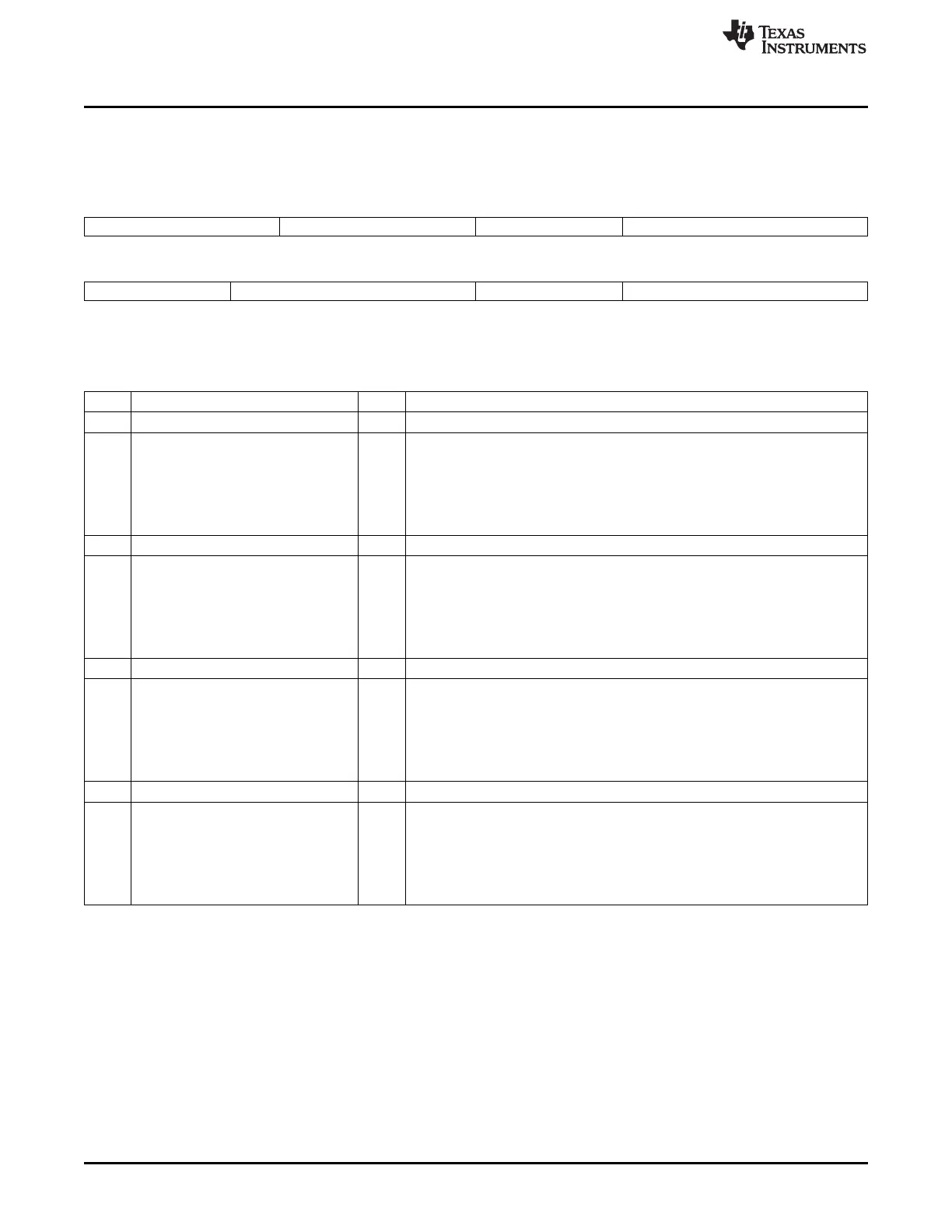

Table 7-69. GPMC_CONFIG5_i Field Descriptions

Bit Field Value Description

31-28 Reserved 0 Reserved

27-24 PAGEBURSTACCESSTIME Delay between successive words in a multiple access

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

Fh 15 GPMC_FCLK cycles

23-21 Reserved 0 Reserved

20-16 RDACCESSTIME Delay between start cycle time and first data valid

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

1Fh 31 GPMC_FCLK cycles

15-13 Reserved 0 Reserved

12-8 WRCYCLETIME Total write cycle time

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

1Fh 31 GPMC_FCLK cycles

7-5 Reserved 0 Reserved

4-0 RDCYCLETIME Total read cycle time

0 0 GPMC_FCLK cycle

1h 1 GPMC_FCLK cycle

⋮ ⋮

1Fh 31 GPMC_FCLK cycles

382

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...