www.ti.com

McASP Registers

22.4.1.32 Transmitter Interrupt Control Register (XINTCTL)

The transmitter interrupt control register (XINTCTL) controls generation of the McASP transmit interrupt

(XINT). When the register bit(s) is set to 1, the occurrence of the enabled McASP condition(s) generates

XINT. The XINTCTL is shown in Figure 22-70 and described in Table 22-43. See Section 22.4.1.33 for a

description of the interrupt conditions.

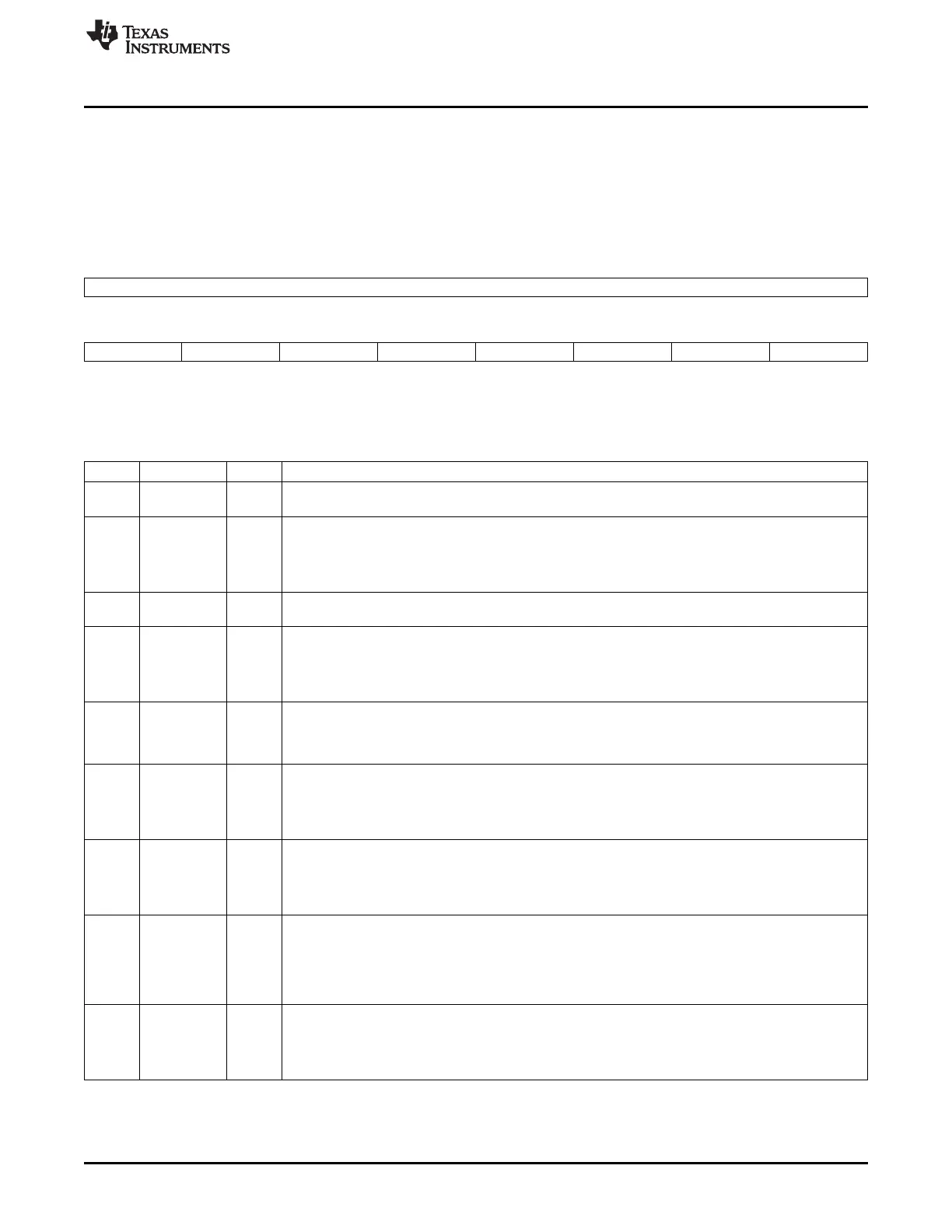

Figure 22-70. Transmitter Interrupt Control Register (XINTCTL)

31 8

Reserved

R-0

7 6 5 4 3 2 1 0

XSTAFRM Reserved XDATA XLAST XDMAERR XCKFAIL XSYNCERR XUNDRN

R/W-0 R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

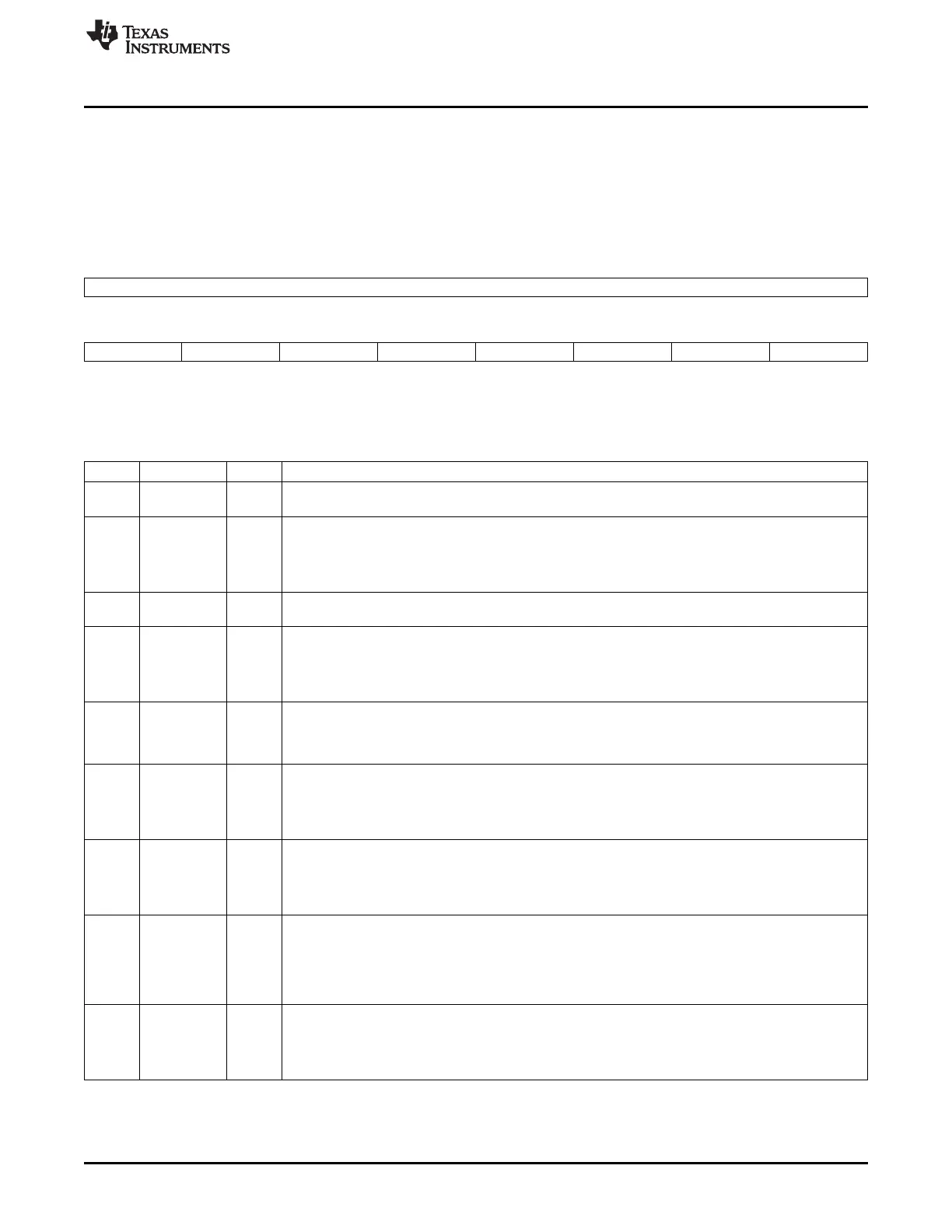

Table 22-43. Transmitter Interrupt Control Register (XINTCTL) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved. The reserved bit location always returns the default value. A value written to this field has no

effect. If writing to this field, always write the default value for future device compatibility.

7 XSTAFRM Transmit start of frame interrupt enable bit.

0 Interrupt is disabled. A transmit start of frame interrupt does not generate a McASP transmit interrupt

(XINT).

1 Interrupt is enabled. A transmit start of frame interrupt generates a McASP transmit interrupt (XINT).

6 Reserved 0 Reserved. The reserved bit location always returns the default value. A value written to this field has no

effect. If writing to this field, always write the default value for future device compatibility.

5 XDATA Transmit data ready interrupt enable bit.

0 Interrupt is disabled. A transmit data ready interrupt does not generate a McASP transmit interrupt

(XINT).

1 Interrupt is enabled. A transmit data ready interrupt generates a McASP transmit interrupt (XINT).

4 XLAST Transmit last slot interrupt enable bit.

0 Interrupt is disabled. A transmit last slot interrupt does not generate a McASP transmit interrupt (XINT).

1 Interrupt is enabled. A transmit last slot interrupt generates a McASP transmit interrupt (XINT).

3 XDMAERR Transmit DMA error interrupt enable bit.

0 Interrupt is disabled. A transmit DMA error interrupt does not generate a McASP transmit interrupt

(XINT).

1 Interrupt is enabled. A transmit DMA error interrupt generates a McASP transmit interrupt (XINT).

2 XCKFAIL Transmit clock failure interrupt enable bit.

0 Interrupt is disabled. A transmit clock failure interrupt does not generate a McASP transmit interrupt

(XINT).

1 Interrupt is enabled. A transmit clock failure interrupt generates a McASP transmit interrupt (XINT).

1 XSYNCERR Unexpected transmit frame sync interrupt enable bit.

0 Interrupt is disabled. An unexpected transmit frame sync interrupt does not generate a McASP transmit

interrupt (XINT).

1 Interrupt is enabled. An unexpected transmit frame sync interrupt generates a McASP transmit interrupt

(XINT).

0 XUNDRN Transmitter underrun interrupt enable bit.

0 Interrupt is disabled. A transmitter underrun interrupt does not generate a McASP transmit interrupt

(XINT).

1 Interrupt is enabled. A transmitter underrun interrupt generates a McASP transmit interrupt (XINT).

3869

SPRUH73H–October 2011–Revised April 2013 Multichannel Audio Serial Port (McASP)

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...