Multimedia Card Registers

www.ti.com

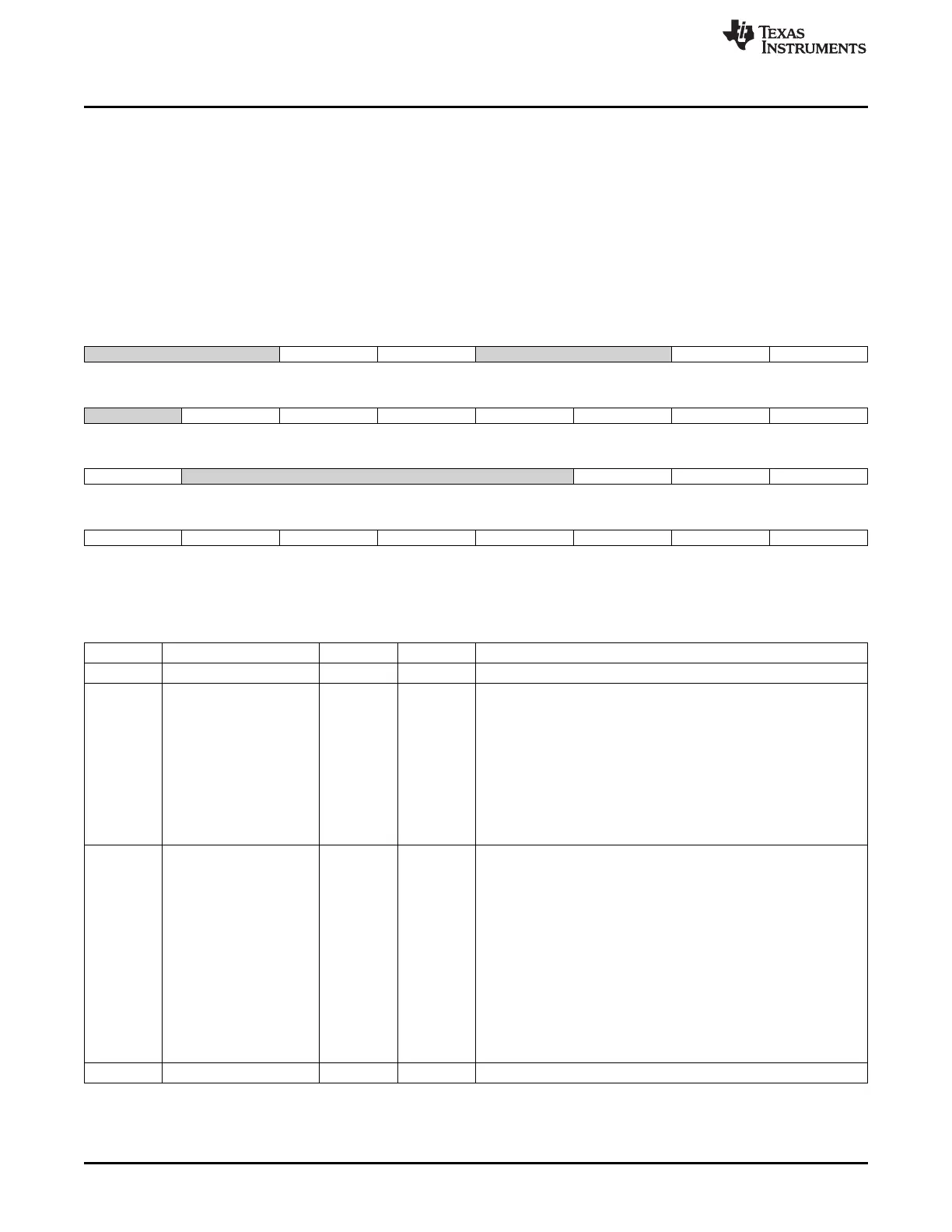

18.5.1.19 SD_STAT Register (offset = 230h) [reset = 0h]

SD_STAT is shown in Figure 18-55 and described in Table 18-38.

The interrupt status regroups all the status of the module internal events that can generate an interrupt.

SD_STAT[31:16] = Error Interrupt Status. SD_STAT[15:0] = Normal Interrupt Status. The error bits are

located in the upper 16 bits of the SD_STAT register. All bits are cleared by writing a 1 to them.

Additionally, bits 15 and 8 serve as special error bits. These cannot be cleared by writing a 1 to them. Bit

15 (ERRI) is automatically cleared when the error causing to ERRI to be set is handled. (that is, when bits

31:16 are cleared, bit 15 will be automatically cleared). Bit 8 (CIRQ) is cleared by writing a 0 to SD_IE[8]

(masking the interrupt) and servicing the interrupt.

Figure 18-55. SD_STAT Register

31 30 29 28 27 26 25 24

Reserved BADA CERR Reserved ADMAE ACE

R-0h R/W-0h R/W-0h R-0h R/W-0h R/W-0h

23 22 21 20 19 18 17 16

Reserved DEB DCRC DTO CIE CEB CCRC CTO

R-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

15 14 13 12 11 10 9 8

ERRI Reserved BSR OBI CIRQ

R-0h R-0h R/W-0h R-0h R-0h

7 6 5 4 3 2 1 0

CREM CINS BRR BWR DMA BGE TC CC

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; R = Read only; W1toCl = Write 1 to clear bit; -n = value after reset

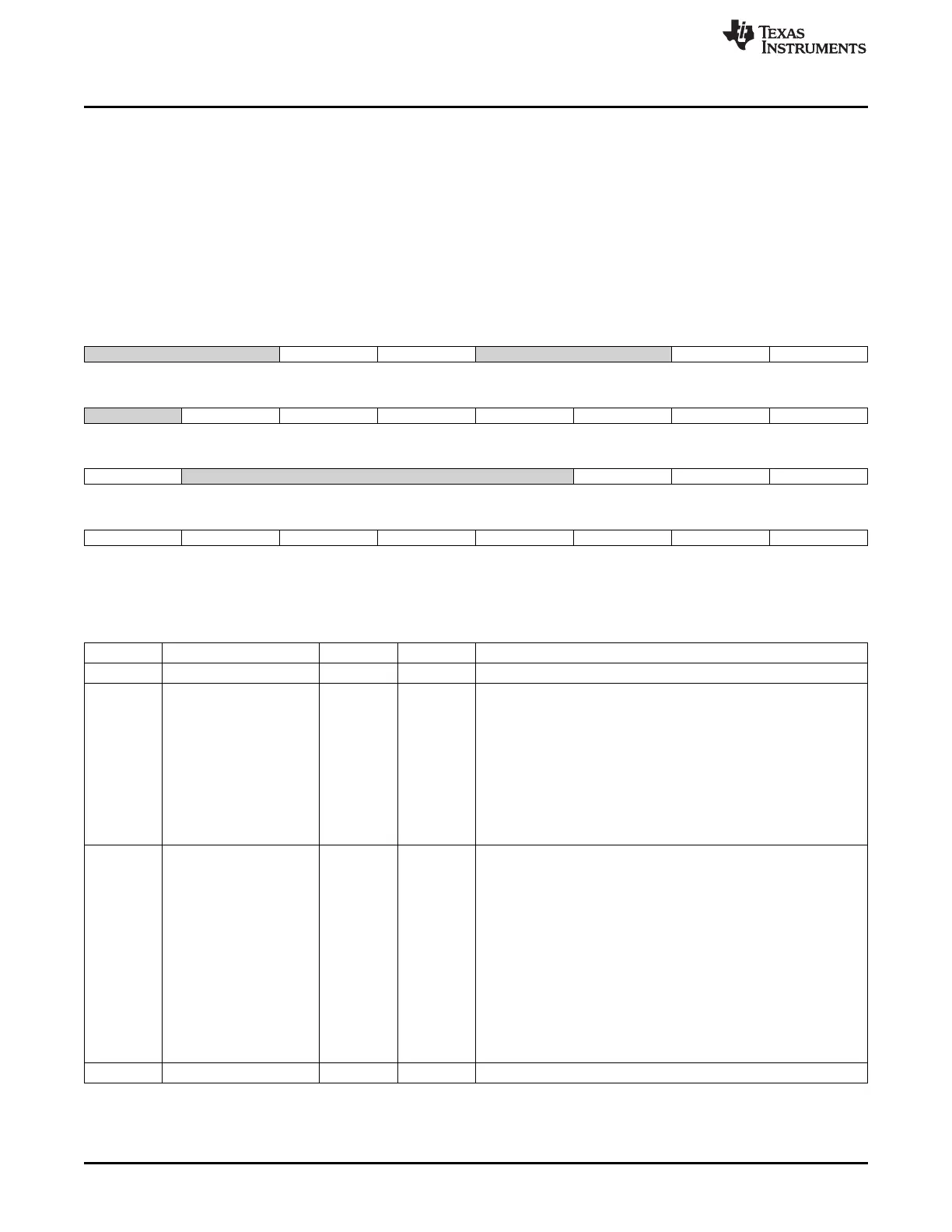

Table 18-38. SD_STAT Register Field Descriptions

Bit Field Type Reset Description

31-30 Reserved R 0h

29 BADA R/W 0h Bad access to data space.

This bit is set automatically to indicate a bad access to buffer when

not allowed: During a read access to the data register (SD_DATA)

while buffer reads are not allowed (SD_PSTATE[11] BRE bit =0).

During a write access to the data register (SD_DATA) while buffer

writes are not allowed (SD_PSTATE[10] BWE bit=0).

0x0(W) = Status bit unchanged

0x0(R) = No interrupt

0x1(W) = Status is cleared.

0x1(R) = Bad access

28 CERR R/W 0h Card error.

This bit is set automatically when there is at least one error in a

response of type R1, R1b, R6, R5 or R5b.

Only bits referenced as type E (error) in status field in the response

can set a card status error.

An error bit in the response is flagged only if corresponding bit in

card status response error SD_CSRE in set.

There is no card error detection for autoCMD12 command.

The host driver shall read SD_RSP76 register to detect error bits in

the command response.

0x0(W) = Status bit unchanged

0x0(R) = No error

0x1(W) = Status is cleared.

0x1(R) = Card error

27-26 Reserved R 0h

3424

Multimedia Card (MMC) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...