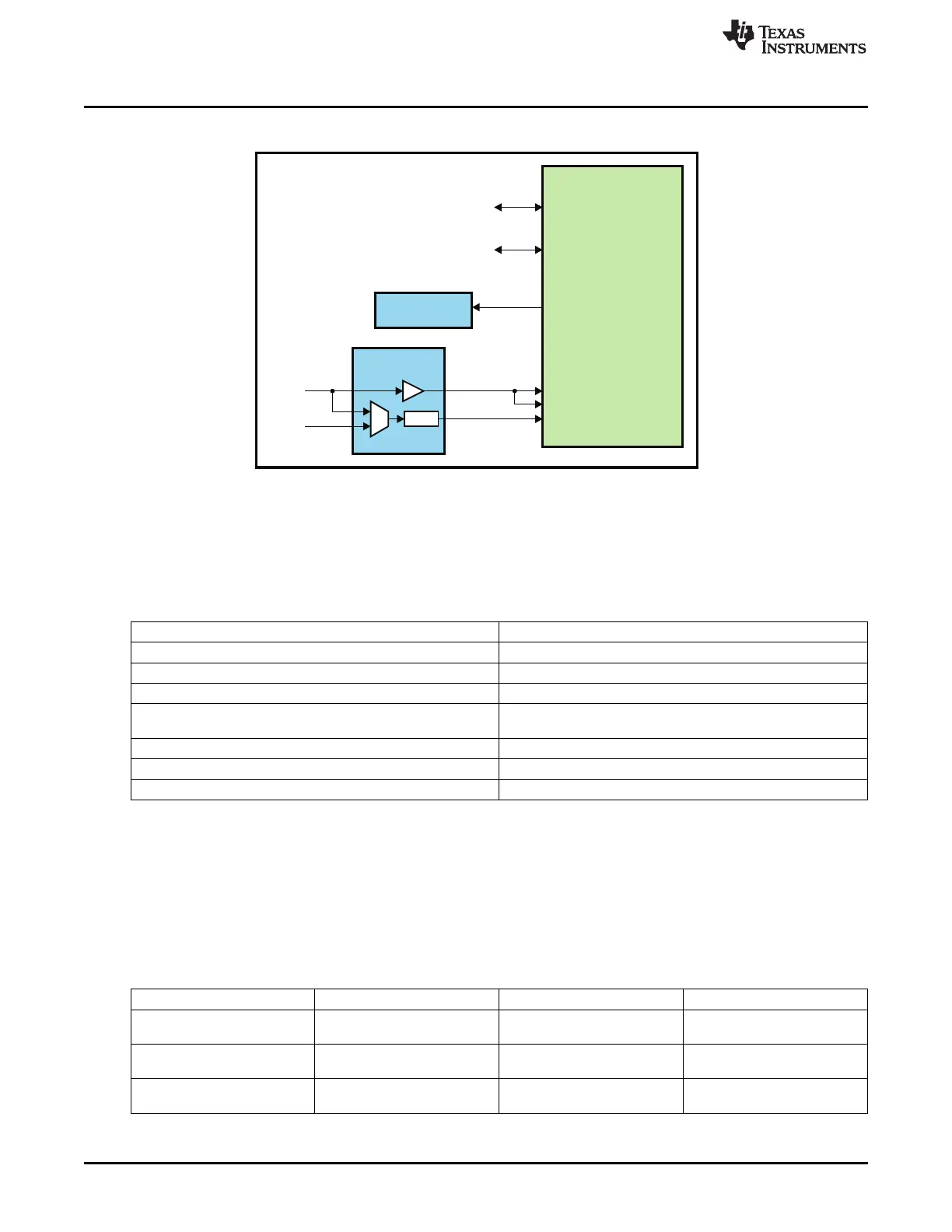

GFX Subsystem

THALIAIRQ

MPU Subsystem

Interrupts

CORECLK

PRCM

Master

Slave

L3 Fast

Interconnect

L3 Fast

Interconnect

MEMCLK

SYSCLK

/1, /2

pd_gfx_gfx_fclk

pd_gfx_gfx_l3_gclk

PER_CLKOUTM2

(192 MHz)

CORE_CLKOUTM4

(200 MHz)

1

0

Integration

www.ti.com

5.2 Integration

Figure 5-1. SGX530 Integration

5.2.1 SGX530 Connectivity Attributes

The general connectivity attributes of the SGX530 are shown in the following table.

Table 5-1. SGX530 Connectivity Attributes

Attributes Type

Power domain GFX Domain

Clock domain SGX_CLK

Reset signals SGX_RST

Idle/Wakeup signals Smart Idle

Initiator Standby

Interrupt request THALIAIRQ (GFXINT) to MPU Subsystem

DMA request None

Physical address L3 Fast slave port

5.2.2 SGX530 Clock and Reset Management

The SGX530 uses separate functional and interface clocks. The SYSCLK is the clock for the slave

interface and runs at the L3F frequency. The MEMCLK is the clock for the memories and master interface

and also runs at the L3F frequency. The CORECLK is the functional clock. It can be sourced from either

the L3F clock (CORE_CLKOUTM4) or from the 192 MHz PER_CLKOUTM2 and can optionally be divided

by 2.

Table 5-2. SGX530 Clock Signals

Clock signal Max Freq Reference / Source Comments

SYSCLK 200 MHz CORE_CLKOUTM4 pd_gfx_gfx_l3_gclk

Interface clock From PRCM

MEMCLK 200 MHz CORE_CLKOUTM4 pd_gfx_gfx_l3_gclk

Memory Clock From PRCM

CORECLK 200 MHz PER_CLKOUTM2 or pd_gfx_gfx_fclk

Functional clock CORE_CLKOUTM4 From PRCM

182

Graphics Accelerator (SGX) SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...